通用门 NAND 和 NOR

可以实现任何可能的布尔函数的逻辑门称为通用门。有两种通用逻辑门,即 NAND 门和 NOR 门。

这两个门被称为通用门,因为它们可以执行任何其他逻辑门的功能,如 AND、OR、NOT、XOR 和 XNOR,而无需任何其他类型的逻辑门。例如,我们可以仅使用 NAND 门或仅使用 NOR 门来执行 AND 门功能。

在本章中,我们将研究通用门的理论和工作原理,即 NAND 门和 NOR 门。

什么是 NAND 门?

NAND 门是一种通用门,基本上是两种基本逻辑门的组合,即 AND 门和非门。它通过将非门连接到与门的输出线来设计,如下图所示。

与非门可以有两条或多条输入线和一条输出线。 NAND 门的输出只有当其所有输入都为高电平或逻辑 1 时才为低电平或逻辑 0。否则,NAND 门的输出为高电平或逻辑 1。

NAND 门基本上是一个执行 AND 门逆运算的逻辑门。

作为通用门,NAND 门可以实现任何可能的布尔函数或任何其他类型逻辑门的运算。

NAND 门的逻辑符号

下图描绘了双输入和三输入 NAND 门的逻辑符号。

此处,输出侧的气泡表示反转运算。

变量 A、B 和 C 表示输入线,变量 Y 表示输出线NAND 门。

NAND 门的真值表

真值表是 NAND 门的输入和输出表,显示它们之间的关系。以下是双输入 NAND 门 −

的真值表| 输入 | 输出 | |

|---|---|---|

| A | B | Y |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

三输入 NAND 门的真值表如下所示 −

| 输入 | 输出 | ||

|---|---|---|---|

| A | B | C | Y |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

从这两个真值表中,我们可以观察到,只有当所有输入都为高电平或逻辑 1 时,NAND 门才会产生低电平或逻辑 0 输出。对于任何其他输入组合,输出为高电平或逻辑 1。

NAND 门的布尔表达式

布尔表达式是一个逻辑函数,它描述 NAND 门的输入和输出之间的逻辑关系。

双输入 NAND 门的布尔表达式如下所示 −

$$\mathrm{Y \: = \: \overline{AB} \: = \: (AB)'}$$

三输入 NAND 门的布尔表达式如下所示,

$$\mathrm{Y \: = \: \overline{ABC} \: = \: (ABC)'}$$

这里,A、B 和 C 是输入变量,Y 是输出变量。

NAND 门的工作原理

下面描述了不同输入组合的双输入 NAND 门的工作原理 −

- 如果 A = 0 且 B = 0,则 NAND 门的输出为 Y = 1。

- 如果 A = 0 且 B = 1,则 NAND 门的输出为 Y = 1。

- 如果 A = 1 且 B = 0,则 NAND 门的输出为 Y = 1。

- 如果 A = 1 且 B = 1,则 NAND 门的输出为 Y = 0。

类似地,三输入 NAND 门的工作原理可解释如下 −

- 如果 A = 0、B = 0 且 C = 0,则 NAND 门的输出为 Y = 1。

- 如果 A = 0、B = 0 且 C = 1,则 NAND 门的输出为 Y = 1。

- 如果 A = 0、B = 1 且 C = 0,则 NAND 门的输出为 Y = 1。

- 如果 A = 0、B = 1 且 C = 1,则 NAND 门的输出为 Y = 1。

- 如果 A = 1、B = 0 且 C = 0,则 NAND 门的输出为 Y = 1。

- 如果 A = 1、B = 0 且 C = 1,则 NAND 门的输出为 Y = 1.

- 如果 A = 1、B = 1 且 C = 0,则 NAND 门的输出为 Y = 1。

- 如果 A = 1、B = 1 且 C = 1,则 NAND 门的输出为 Y = 0。

这都是关于 NAND 门针对不同输入组合的操作。

同样值得注意的是,在本章中,我们仅通过考虑两个和三个输入变量来讨论 NAND 门的理论。但相同的逻辑和理论适用于任何数量的输入。

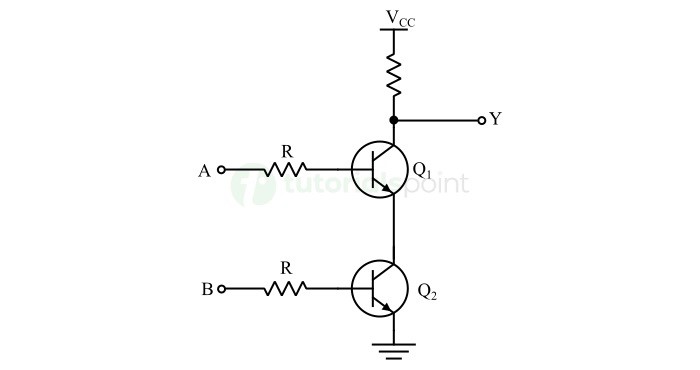

使用晶体管的 NAND 门

我们可以使用 BJT 晶体管实现 NAND 门逻辑。这样的 NAND 门被称为晶体管 NAND 门。

下图显示了双输入 NAND 门的晶体管电路图。

晶体管 NAND 门的工作原理

下面将解释这种晶体管 NAND 门在不同输入组合下的工作原理 −

当输入 A 和 B 都连接到低信号时,晶体管 Q1 和 Q2 充当开路开关。整个电源电压将出现在输出线Y上。因此,对于这种输入组合,电路的输出为高电平或逻辑1。

当输入A处于低电平而输入B处于高电平时,晶体管Q1充当断开开关,晶体管Q2充当闭合开关。在这种情况下,电源和接地端子之间没有直接连接。因此,整个电源电压将出现在输出端Y上,使其为高电平或逻辑1。

当输入A处于高电平而输入B处于低电平时,晶体管Q1充当闭合开关,晶体管Q2充当断开开关。同样,电源和接地端子之间断开。对于这种输入组合,整个电源电压将出现在输出线上,并将输出设置为高电平或逻辑 1。

当两个输入都连接到高电平或逻辑 1 信号时,两个晶体管都将打开,并将输出线直接连接到接地端子,即低电位。这使电路的输出为低电平或逻辑 0。

因此,只有当所有输入都为高电平或逻辑 1 时,该电路的输出才为低电平或逻辑 0,否则输出为高电平或逻辑 1。因此,该电路实现了 NAND 门逻辑。

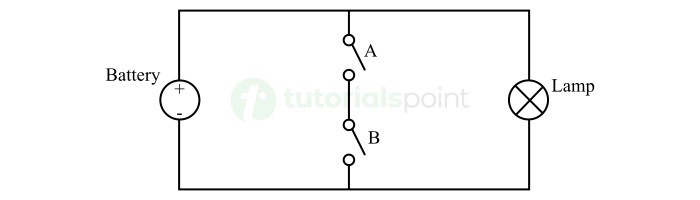

使用开关的 NAND 门

我们还可以使用电开关、电池和灯来实现 NAND 门。下图显示了使用开关的双输入 NAND 门的电路图。

在此开关电路中,当开关 A 和 B 都关闭时,电流会绕过灯而流动,形成短路。因此,没有电流会流过灯,灯也不会发光。这表示低或逻辑 0 输出。

对于任何其他开关布置,例如 A 关闭而 B 打开、A 打开而 B 关闭或 A 和 B 打开。没有短路路径,整个电流将流过灯,使其打开。这表示高电平或逻辑 1 输出。

因此,只有当两个开关都关闭时,此开关电路的输出才为低电平或逻辑 0,否则输出为高电平或逻辑 1。因此,此电路充当 NAND 门。

我们可以添加更多与 A 和 B 串联的开关,以实现更高阶的 NAND 门。

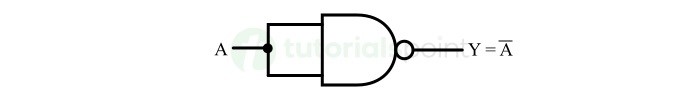

NAND 门作为反相器

NAND 门也可用作反相器门。为此,将其所有输入连接在一起,并将要反相的输入信号施加到公共端子,如下图所示。

NAND 门的应用

NAND 门用于各种数字和自动化系统。其中一些列于下方 −

- 报警电路

- 蜂鸣器和防盗装置

- 自动温度调节系统

- 安全系统

- 自动门窗等

以上就是有关 NAND 门及其工作原理和应用的全部内容。现在让我们讨论另一种通用门(即 NOR 门)的理论。

什么是 NOR 门?

NOR 门 是另一种通用门,用于数字电子技术中实现布尔函数。它是两种基本逻辑门(即或门和非门)的组合。 NOR 门的设计方法是将 NOT 门连接到输出线,最终输出取自 NOT 门的输出线,如下图所示。

作为通用逻辑门,它可以单独用于实现任何可能的布尔函数或其他逻辑门。

NOR 门可以有两条或更多条输入线和一条输出线。仅当所有输入均为低电平或逻辑 0 时,NOR 门的输出才为高电平或逻辑 1。对于所有其他输入组合,NOR 门的输出均为低电平或逻辑 0。

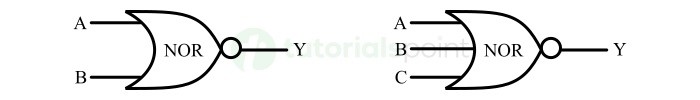

NOR 门的逻辑符号

下图显示了二输入和三输入 NOR 门的逻辑符号。

此处,A、B 和 C 为输入线,Y 为输出线。输出端的气泡表示反转操作。

NOR 门的真值表

NOR 门的真值表指定了不同输入组合的输出。双输入 NOR 门的真值表如下所示 −

| 输入 | 输出 | |

|---|---|---|

| A | B | Y |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

以下是三输入或非门的真值表 −

| 输入 | 输出 | ||

|---|---|---|---|

| A | B | C | Y |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

从这些真值表中,我们可以观察到,只有当所有输入都为低或逻辑 0 时,或非门的输出才为高或逻辑 1,否则输出为低或逻辑 0。

或非门的工作原理

下面解释了所有可能输入组合的双输入或非门的运行 −

- 如果 A = 0 且 B = 0,或非门的输出为 Y = 1。

- 如果 A = 0 且 B = 1,或非门的输出为 Y = 0。

- 如果 A = 1 且 B = 0,或非门的输出为 Y = 0。

- 如果 A = 1 且 B = 1,或非门的输出为 Y = 0。

类似地,三输入或非门的运行NOR 门可以描述如下 −

- 如果 A = 0、B = 0 且 C = 0,则 NOR 门的输出为 Y = 1。

- 如果 A = 0、B = 0 且 C = 1,则 NOR 门的输出为 Y = 0。

- 如果 A = 0、B = 1 且 C = 0,则 NOR 门的输出为 Y = 0。

- 如果 A = 0、B = 1 且 C = 1,则 NOR 门的输出为 Y = 0。

- 如果 A = 1、B = 0 且 C = 0,则 NOR 门的输出为 Y = 0。

- 如果 A = 1、B = 1 且 C = 0,则 NOR 门的输出为 Y = 0。

- 如果 A = 1、B = 1 且 C = 1,则 NOR 门的输出为 Y = 0。

从此讨论中,我们可以观察到,当 NOR 门的所有输入均为低或逻辑 0 时,它会产生高或逻辑 1 输出。

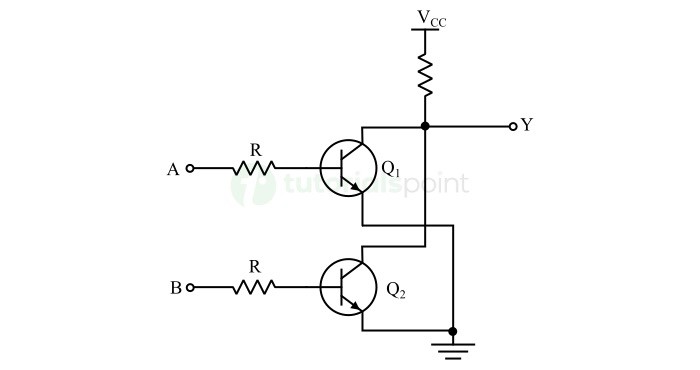

使用晶体管的 NOR 门

我们可以使用晶体管实现 NOR 门。下图显示了使用晶体管的双输入 NOR 门的电路图。该电路称为晶体管或非门。

晶体管或非门的工作原理

晶体管或非门的工作原理如下 −

当输入 A 和 B 都为低电平时,晶体管 Q1 和 Q2 不导通并充当断开开关。在这种情况下,输出线 Y 将直接连接到电源。因此,整个电源电压将出现在输出端。这使得电路的输出为高电平或逻辑 1。

当输入 A 连接到低电平并且输入 B 连接到高电平信号时,晶体管 Q1 将充当断开开关,而晶体管 Q2 将充当闭合开关。在这种情况下,输出线 Y 将通过晶体管 Q2 直接连接到接地端子。这会导致输出线上出现低电平信号。

当输入 A 连接到高电平并且输入 B 连接到低电平信号时,晶体管 Q1 将导通,而晶体管 Q2 将充当断开开关。在这种情况下,输出线直接连接到接地端子。因此,输出为低电平或逻辑 0。

当输入 A 和 B 都连接到高电平信号时,晶体管 Q1 和 Q2 都将充当闭合开关,并将输出线直接连接到接地端子。在这种情况下,输出也为低电平或逻辑 0。

从此讨论中,我们可以观察到,该晶体管电路实现了 NOR 逻辑,因此称为晶体管 NOR 门。

我们可以在电路中添加更多晶体管以获得更高阶的 NOR 门。

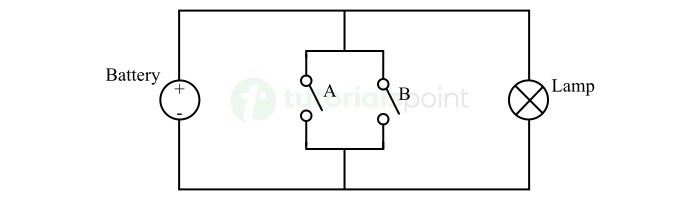

使用开关的 NOR 门

我们还可以使用电开关实现 NOR 门。下图显示了使用开关的双输入 NOR 门的电路图。

在此电路中,如果开关 A 和 B 都打开,则整个电流都会流过灯并将其打开。这表示输出的高或逻辑 1 状态。

如果两个或任何一个开关都关闭,则电流会绕过灯而流动。在这种情况下,灯不会发光,并表示输出的低或逻辑 0 状态。

因此,只有当该开关电路的两个输入都为低(即打开开关)时,其输出才为高或逻辑 1,否则输出为低或逻辑 0。

因此,该电路实现了 NOR 门的操作和逻辑。

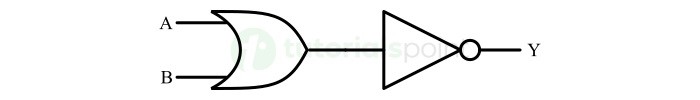

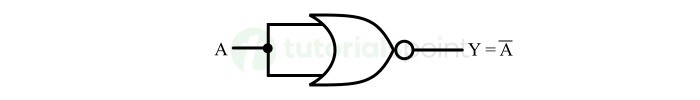

NOR 门作为反相器

NOR 门也可用作反相器门。要将 NOR 门用作反相器,请将其所有输入连接在一起,并将输入信号施加到公共端子,如下图所示。

NOR 门的应用

NOR 门用于许多数字系统中。下面列出了 NOR 门的一些常见应用 −

- 各种数字系统

- 工业自动化和控制系统

- 交通控制系统

- 报警电路

- 数字算术电路,如加法器和减法器等。

结论

总之,通用逻辑门是一种可以实现任何可能的布尔函数或其他逻辑门而无需任何其他类型逻辑门的逻辑门。在数字电子技术中,有两种通用逻辑门,即 NAND 门和 NOR 门。

在本章中,我们解释了这两种通用门的理论、工作原理和应用。这里我们仅介绍了两输入和三输入的 NAND 门和 NOR 门,但相同的理论和解释对于具有三个以上输入的 NAND 门和 NOR 门同样有效。