数字电子技术 - 串行二进制加法器

在数字电子技术中,二进制加法器是一种组合逻辑电路,可执行两个或多个二进制数字的加法。二进制加法是基于布尔代数加法定律进行的,即

$$\mathrm{0 \: + \: 0 \: = \: 0}$$

$$\mathrm{0 \: + \: 1 \: = \: 1}$$

$$\mathrm{1 \: + \: 0 \: = \: 1}$$

$$\mathrm{1 \: + \: 1 \: = \: 0}$$

二进制加法器分为两种类型,即串行二进制加法器和并行二进制加法器。

在本教程中,我们将讨论串行二进制加法器、其定义、逻辑电路图和操作。因此,让我们从串行二进制加法器的基本介绍开始。

什么是串行二进制加法器?

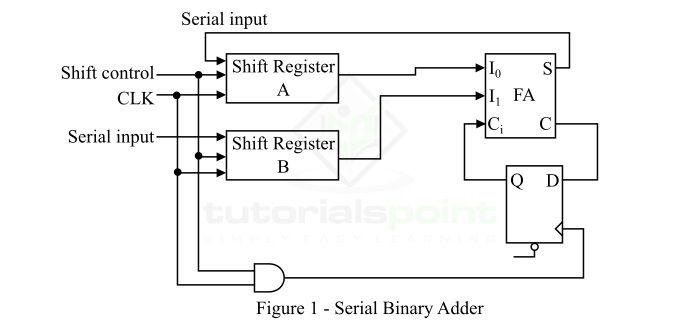

串行二进制加法器是一种二进制加法器电路,用于以串行形式添加二进制数。在串行加法器中,两个串行相加的二进制数分别存储在两个移位寄存器中,即移位寄存器A和移位寄存器B。

串行二进制加法器的逻辑电路图如图1所示。

串行加法器电路中各元件的功能如下 −

全加器

全加器是一种数字组合逻辑电路,它可以将三个二进制数字相加,并产生两个输出位,即和位和进位。在串行二进制加法器电路中,全加器每次将一对位相加。

移位寄存器

一组可以存储几位数据的触发器称为移位寄存器。在串行二进制加法器中,使用两个移位寄存器,其中一个用于存储被加数位,另一个用于存储二进制数的加法。

D 触发器

在串行加法器中,D 触发器用于存储进位输出位。此 D 触发器的输出用作下一阶段加法的进位输入。

串联二进制加法器的操作

在串行二进制加法器电路中,使用全加器电路一次将二进制数字(位)相加一对。全加器产生的进位被传输到 D 触发器。因此,此 D 触发器的输出随后用作下一对有效位的进位输入。和位 S 被传输到第三个移位寄存器。现在,让我们详细了解串行二进制加法器的操作。

一开始,移位寄存器 A 存储给定二进制数的被加数位,移位寄存器 B 存储加数位。最初,D 触发器被清除为 0,因此不存在进位位。移位寄存器 A 和 B 的输出在输入 I0 和 I1 处向全加器电路提供一对有效位。移位控制用于启用移位寄存器 A 和 B 以及进位触发器。

因此,在每个时钟脉冲处,寄存器 A 和 B 向右移位,全加器电路输出 S 的和位进入移位寄存器 A 的最左侧。因此,对于每个后续时钟脉冲,一个新的和位被传输到移位寄存器 A,一个新的进位位被传输到 D 触发器的输出 Q。此过程持续进行,直到移位控制被禁用。

因此,串行形式的两个二进制数的加法是通过将一对位与前一个进位一起提供给全加器电路,并一次将一个和位传输到移位寄存器 A 中来实现的。

现在,我们可以总结串行二进制加法器的工作过程如下 −

- 最初,移位寄存器 A 和进位触发器设置为 0,并从寄存器 B 中添加第一个数字。

- 当寄存器 B 通过全加器移位时,第二个数字通过其串行输入传输给它。

- 然后将第二个数字添加到寄存器 A 的数字中,同时通过串行输入将第三个数字传输到寄存器 B 中。

此过程重复执行,以串行形式执行两个、三个或更多二进制数的加法,并将总和结果累积在移位寄存器 A 中。