数字电子技术 - 移位寄存器

触发器是 1 位存储单元,可用于存储数字数据。为了增加位数的存储容量,我们必须使用一组触发器。这样的一组触发器称为寄存器。n 位寄存器将由 n 个触发器组成,并且能够存储 n 位 个字。

寄存器中的二进制数据可以在寄存器内从一个触发器移动到另一个触发器。允许此类数据传输的寄存器称为移位寄存器。移位寄存器有四种操作模式。

- 串行输入 - 串行输出 (SISO) 移位寄存器

- 串行输入 - 并行输出 (SIPO) 移位寄存器

- 并行输入 - 串行输出 (PISO) 移位寄存器

- 并行输入 - 并行输出 (PIPO) 移位寄存器

串行输入 - 串行输出 (SISO) 移位寄存器

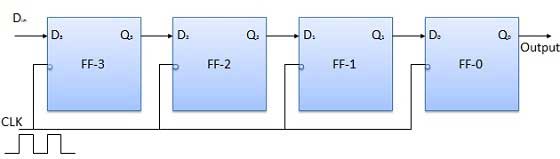

让所有触发器最初处于复位状态,即 Q3 = Q2 = Q1 = Q0 = 0。如果将四位二进制数 1 1 1 1 输入到寄存器中,则应将此数字应用于 Din 位,首先应用 LSB 位。 FF-3 的 D 输入,即 D3 连接到串行数据输入 Din。FF-3 的输出,即 Q3 连接到下一个触发器的输入,即 D2,依此类推。

框图

操作

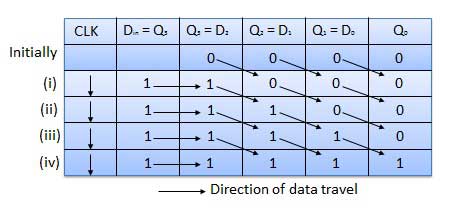

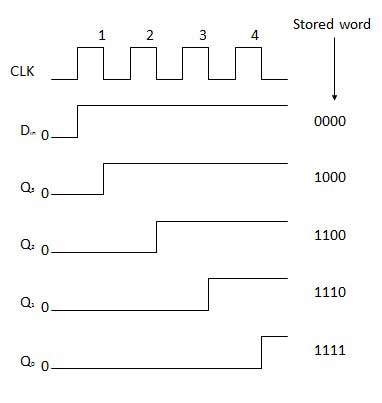

在施加时钟信号之前,让 Q3 Q2 Q1 Q0 = 0000,并将要输入的数字的 LSB 位应用于 Din。因此 Din = D3 = 1。应用时钟。在时钟的第一个下降沿,FF-3 被设置,寄存器中存储的字为 Q3 Q2 Q1 Q0 = 1000。

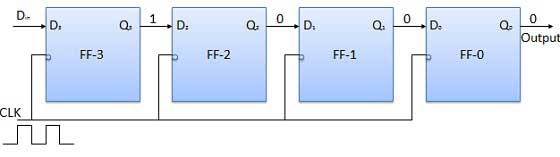

将下一位应用于 Din。因此 Din = 1。一旦时钟的下一个负沿到达,FF-2 将设置,存储的字将更改为 Q3 Q2 Q1 Q0 = 1100。

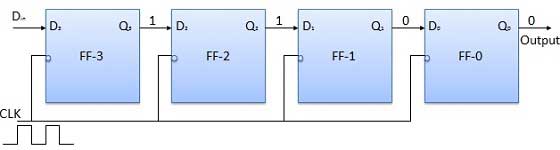

将下一个要存储的位(即 1)应用于 Din。应用时钟脉冲。一旦第三个负时钟沿到达,FF-1 将设置,输出将修改为 Q3 Q2 Q1 Q0 = 1110。

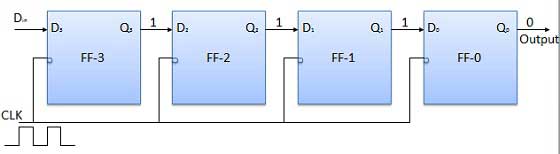

同样,当 Din = 1 且第四个负时钟沿到达时,寄存器中存储的字为 Q3 Q2 Q1 Q0 = 1111。

真值表

波形

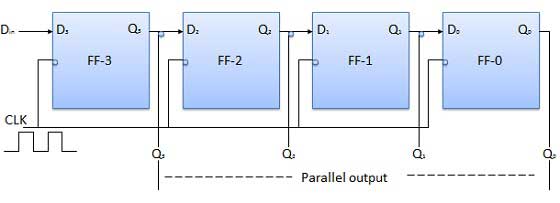

串行输入 - 并行输出 (SIPO) 移位寄存器

- 在此类操作中,数据以串行方式输入并以并行方式取出。

- 数据逐位加载。只要数据正在加载,输出就会被禁用。

- 一旦数据加载完成,所有触发器都包含其所需的数据,输出就会启用,以便所有加载的数据同时在所有输出线上可用。

- 加载四位字需要 4 个时钟周期。因此,SIPO 模式的运行速度与 SISO 模式相同。

框图

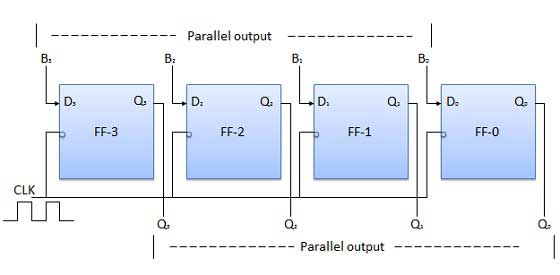

并行输入 - 串行输出 (PISO) 移位寄存器

- 数据位以并行方式输入。

- 下面显示的电路是一个四位并行输入串行输出寄存器。

- 前一个触发器的输出通过组合电路连接到下一个触发器的输入。

- 二进制输入字 B0、B1、B2、B3 通过相同的组合电路应用。

- 该电路可以工作在两种模式下,即 -移位模式或加载模式。

加载模式

当移位/加载条线为低电平 (0) 时,AND 门 2、4 和 6 变为活动状态,它们将 B1、B2、B3 位传递到相应的触发器。在时钟的低电平沿,二进制输入 B0、B1、B2、B3 将加载到相应的触发器中。因此,并行加载发生。

移位模式

当移位/加载条线为低电平 (1) 时,AND 门 2、4 和 6 变为非活动状态。因此,数据的并行加载变得不可能。但 AND 门 1、3 和 5 变为活动状态。因此,在施加时钟脉冲时,数据从左向右逐位移位。因此,并行输入串行输出操作就发生了。

框图

并行输入 - 并行输出 (PIPO) 移位寄存器

在此模式下,4 位二进制输入 B0、B1、B2、B3 分别应用于四个触发器的数据输入 D0、D1、D2、D3。一旦施加负时钟沿,输入二进制位将同时加载到触发器中。加载的位将同时出现在输出侧。仅时钟脉冲对于加载所有位至关重要。

框图

双向移位寄存器

- 如果二进制数左移一位,则相当于将原始数乘以 2。同样,如果二进制数右移一位,则相当于将原始数除以 2。

- 因此,如果我们想使用移位寄存器对给定的二进制数进行乘法和除法,那么我们应该能够向左或向右移动数据。

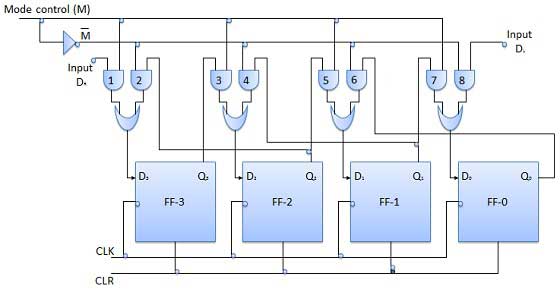

- 这样的寄存器称为双向寄存器。图中显示了一个四位双向移位寄存器。

- 有两个串行输入,即串行右移数据输入 DR 和串行左移数据输入 DL,以及一个模式选择输入 (M)。

框图

操作

| Sr.No | 条件 | 操作 |

|---|---|---|

| 1 | M = 1 −右移操作 |

如果 M = 1,则 AND 门 1、3、5 和 7 启用,而其余 AND 门 2、4、6 和 8 将被禁用。 在时钟脉冲的作用下,DR 处的数据从 FF-3 到 FF-0 逐位向右移位。因此,当 M = 1 时,我们得到串行右移操作。 |

| 2 | 当 M = 0 −左移操作 |

当模式控制 M 连接到 0 时,AND 门 2、4、6 和 8 启用,而 1、3、5 和 7 禁用。 在时钟脉冲的作用下,DL 处的数据从 FF-0 逐位左移到 FF-3。因此,当 M = 0 时,我们得到串行右移操作。 |

通用移位寄存器

只能在一个方向上移位数据的移位寄存器称为单向移位寄存器。可以双向移位数据的移位寄存器称为双向移位寄存器。应用相同的逻辑,可以双向移位数据以及并行加载数据的移位寄存器称为通用移位寄存器。移位寄存器能够执行以下操作 −

- 并行加载

- 左移

- 右移

模式控制输入连接到逻辑 1 以进行并行加载操作,而连接到 0 以进行串行移位。模式控制引脚接地,通用移位寄存器用作双向寄存器。对于串行左移操作,输入应用于串行输入,该串行输入进入图中所示的与门 1。而对于右移操作,串行输入应用于 D 输入。

框图