数字电子技术 - 计数器

计数器是一种顺序电路。用于计数脉冲的数字电路称为计数器。计数器是触发器最广泛的应用。它是一组施加时钟信号的触发器。计数器有两种类型。

- 异步或脉动计数器

- 同步计数器

异步或脉动计数器

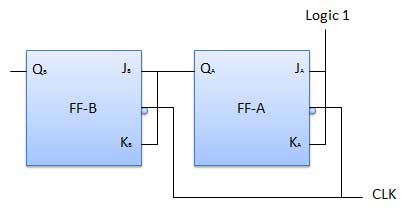

图中显示了 2 位脉动计数器的逻辑图。正在使用切换 (T) 触发器。但是我们也可以使用 JK 触发器,将 J 和 K 永久连接到逻辑 1。外部时钟应用于触发器 A 的时钟输入,QA 输出应用于下一个触发器(即 FF-B)的时钟输入。

逻辑图

操作

| Sr.No | 条件 | 操作 |

|---|---|---|

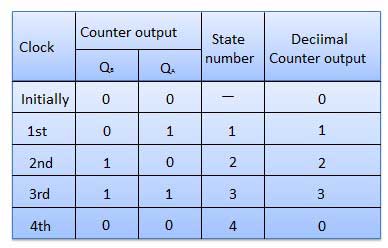

| 1 | 最初让FF 处于复位状态 | QBQA 最初 = 00 |

| 2 | 第一个负时钟沿之后 |

一旦应用第一个负时钟沿,FF-A 将切换,QA 将等于 1。 QA 连接到 FF-B 的时钟输入。由于 QA 已从 0 变为 1,因此 FF-B 将其视为正时钟沿。 QB 没有变化,因为 FF-B 是负沿触发的 FF。 第一个时钟脉冲后,QBQA = 01。 |

| 3 | 第二个负时钟沿之后 |

第二个负时钟沿到来时,FF-A 再次切换,QA = 0。 QA 的变化充当 FF-B 的负时钟沿。因此它也会切换,QB 将为 1。 第二个时钟脉冲后,QBQA = 10。 |

| 4 | 第 3 个负时钟沿之后 |

第 3 个负时钟沿到来时,FF-A 再次切换,QA 从 0 变为 1。 由于这是一个正向变化,FF-B 不会对其作出响应并保持不活动状态。因此 QB 不变并继续等于 1。 第三个时钟脉冲后,QBQA = 11。 |

| 5 | 第 4 个负时钟沿后 |

第 4 个负时钟沿到来时,FF-A 再次切换,QA 从 0 变为 1。 QA 中的这个负变化充当 FF-B 的时钟脉冲。因此,它会切换以将 QB 从 1 更改为 0。 第四个时钟脉冲后,QBQA = 00。 |

真值表

同步计数器

如果"时钟"脉冲同时应用于计数器中的所有触发器,则这种计数器称为同步计数器。

2 位同步递增计数器

FF-A 的 JA 和 K

逻辑图

操作

| Sr.No | 条件 | 操作 |

|---|---|---|

| 1 | 最初让两个 FF 都处于复位状态 | QBQA = 00最初。 |

| 2 | 第一个负时钟沿之后 |

一旦应用第一个负时钟沿,FF-A 将切换,QA 将从 0 变为 1。 但在应用负时钟沿的瞬间,QA ,JB = K 第一个时钟脉冲后,QBQA = 01。 |

| 3 | 第二个负时钟沿之后 |

第二个负时钟沿到来时,FF-A 再次切换,QA 从 1 变为 0。 但此时 QA 为 1。因此 JB = K 第二个时钟脉冲后,QBQA = 10。 |

| 4 | 第三个时钟下降沿后 |

在第三个时钟下降沿应用时,FF-A 将从 0 切换到 1,但 FF-B 的状态没有变化。 第三个时钟脉冲后,QBQA = 11。 |

| 5 | 在第 4 个负时钟沿之后 |

在施加下一个时钟脉冲时,QA 将从 1 变为 0,因为 QB 也将从 1 变为 0。 在第四个时钟脉冲之后,QBQA = 00。 |

计数器的分类

根据计数方式,同步或异步计数器分类如下 −

- 加计数器

- 减计数器

- 加/减计数器

加/减计数器

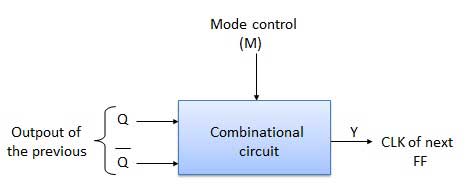

加计数器和减计数器组合在一起可获得上/下计数器。还提供模式控制 (M) 输入以选择上或下模式。需要设计一个组合电路并将其用于每对触发器之间以实现上/下操作。

上/下计数器的类型

上/下计数器有两种类型 −

- 上/下波纹计数器

- 上/下同步计数器

上/下波纹计数器

在上/下波纹计数器中,所有 FF 都以切换模式运行。因此,应使用 T 触发器或 JK 触发器。LSB 触发器直接接收时钟。但是,每个其他 FF 的时钟均来自前一个 FF 的 (Q = Q bar) 输出。

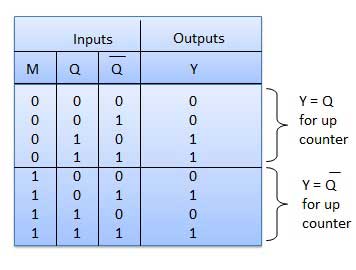

- 向上计数模式 (M=0) − 如果要实现向上计数,则前一个 FF 的 Q 输出将连接到下一阶段的时钟。对于此模式,模式选择输入 M 为逻辑 0 (M=0)。

- 向下计数模式 (M=1) − 如果 M = 1,则前一个 FF 的 Q bar 输出将连接到下一个 FF。这将使计数器在计数模式下运行。

示例

3 位二进制向上/向下波纹计数器。

- 3 位 − 因此需要三个 FF。

- 向上/向下 −因此,模式控制输入必不可少。

- 对于脉动上升计数器,前一个 FF 的 Q 输出连接到下一个 FF 的时钟输入。

- 对于脉动上升计数器,前一个 FF 的 Q 输出连接到下一个 FF 的时钟输入。

- 对于脉动下降计数器,前一个 FF 的 Q bar 输出连接到下一个 FF 的时钟输入。

- 让前一个 FF 的 Q 和 Q bar 输出的选择由模式控制输入 M 控制,这样,如果 M = 0,则向上计数。因此将 Q 连接到 CLK。如果 M = 1,则向下计数。因此将 Q 栏连接到 CLK。

框图

真值表

操作

| Sr.No | 条件 | 操作 |

|---|---|---|

| 1 | 情况 1 − 当 M = 0(向上计数模式)时 |

如果 M = 0 且 M bar = 1,则图中的 AND 门 1 和 3 将启用,而 AND 门 2 和 4 将禁用。 因此 QA 连接到 FF-B 的时钟输入,QB 连接到 FF-C 的时钟输入。 这些连接与普通向上计数器的连接相同。因此,当 M = 0 时,电路作为向上计数器工作。 |

| 2 | 情况 2 −当 M = 1 时(向下计数模式) |

如果 M = 1,则图中的 AND 门 2 和 4 被启用,而 AND 门 1 和 3 被禁用。 因此 QA 杆连接到 FF-B 的时钟输入,QB 杆连接到 FF-C 的时钟输入。 这些连接将产生一个向下计数器。因此,当 M = 1 时,电路用作向下计数器。 |

模数计数器(MOD-N 计数器)

2 位纹波计数器称为 MOD-4 计数器,3 位纹波计数器称为 MOD-8 计数器。因此,一般来说,n 位纹波计数器称为模数-N 计数器。其中,MOD 数 = 2n。

模数类型

- 2 位上或下 (MOD-4)

- 3 位上或下 (MOD-8)

- 4 位上或下 (MOD-16)

计数器的应用

- 频率计数器

- 数字时钟

- 时间测量

- A 至 D 转换器

- 分频器电路

- 数字三角波发生器。