数字电子技术 - 半减法器

在数字电子技术中,减法器是一种组合逻辑电路,可以执行两个数字(二进制数)的减法并产生它们之间的差值。它是一个组合电路,这意味着它的输出仅取决于其当前输入。虽然在实践中,两个二进制数的减法是通过取减数的 1 或 2 的补码并将其添加到被减数来实现的。

这样,二进制数的减法运算可以转换为简单的加法运算,从而使硬件构造简单且成本更低。减法器有两种类型,即半减法器和全减法器。

在本文中,我们将讨论半减法器、其基本定义、电路图、真值表、特征方程等。因此,让我们从半减法器的基本定义开始。

什么是半减法器?

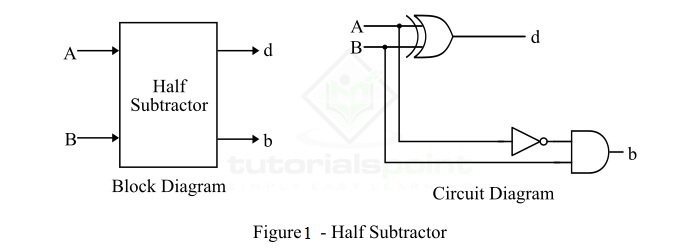

半减法器是一种具有两个输入和两个输出(即差值和借位)的组合逻辑电路。半减法器产生输入端两个二进制位之间的差值,并产生借位输出(如果有)。在减法(A-B)中,A 称为被减数位,B 称为减数位。半减法器的框图和逻辑电路图如图 1 所示。

因此,从逻辑电路图中可以清楚地看出,半减法器可以用异或门、非门和与门来实现。

在图 1 所示的半减法器中,A 和 B 是输入,d 和 b 是输出。其中,d 表示差值,b 表示借位输出。借位输出 (b) 是告知下一阶段已借入 1 的信号。

半减法器的工作原理

现在,让我们了解半减法器电路的工作原理。半减器根据二进制减法的规则执行操作以查找两个二进制数字之间的差值,如下所示 −

只要被减数位 (A) 大于或等于减数位 (B),即 A ≥ B,则输出借位 b 为零 (0)。当 A = 0 且 B = 1 时,输出借位为 1。

从半减器的逻辑电路图中可以清楚地看出,差位 (d) 是通过两个输入 A 和 B 的异或运算获得的,借位是通过被减数 (A') 的补码与减数 (B) 的与运算获得的。

半减器的真值表

以下是半减器 −

的真值表| 输入 | 输出 | ||

|---|---|---|---|

| A | B | D (Difference) | B (Borrow) |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

半减法器的 K-Map

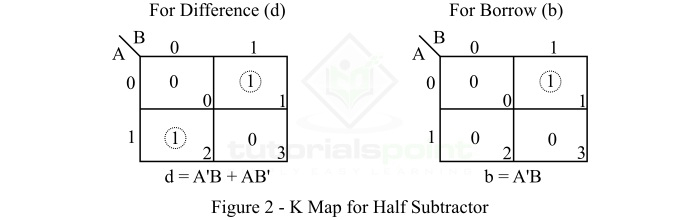

我们可以使用 K-Map(或卡诺图)这种简化布尔代数的方法来确定差位 (d) 和输出借位 (b) 的方程。

半减法器的 K-Map 简化如图 2 所示。

半减法器的特征方程

半减法器的特征方程,即差位 (d) 和输出借位 (b) 的方程,是通过遵循二进制减法规则获得的。这些方程式如下所示 −

半减法器的差分位 (d) 由两个输入 A 和 B 进行异或运算得出。因此,

$$\mathrm{Difference, \: d \: = \: A \oplus B \: = \: A'B \: + \: AB'}$$

半减法器的借位 (b) 是 A' (A 的补码) 和 B 的 AND。因此,

$$\mathrm{Borrow, \: b \: = \: A'B}$$

半减法器的应用

以下是半减法器的一些重要应用−

- 半减器用于处理器的 ALU(算术逻辑单元)。

- 半减器也可用于放大器以补偿声音失真。

- 它也用于降低无线电信号或音频信号的强度。

- 半减器也用于增加或减少运算符。

结论

从上面的讨论中,我们可以得出结论,半减器是一种组合逻辑电路,可以计算两个二进制数字之间的差值。当一个二进制数从另一个二进制数中减去时,半减器只能用于从被减数的 LSB(最低有效位)中减去减数的 LSB(最低有效位)。