时钟信号和触发

在本章中,我们将逐一讨论时钟信号和触发类型。

时钟信号

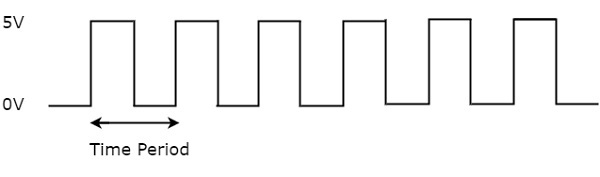

时钟信号是一种周期性信号,其开启时间和关闭时间不必相同。当时钟信号的开启时间和关闭时间相同时,我们可以将其表示为方波。下图显示了此时钟信号。

在上图中,方波被视为时钟信号。该信号在逻辑高电平(5V)保持一段时间,在逻辑低电平(0V)保持相同时间。这种模式在一段时间内重复。在这种情况下,时间周期将等于 ON 时间的两倍或 OFF 时间的两倍。

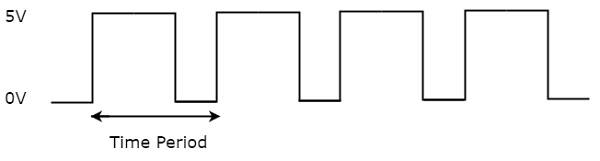

当 ON 时间和 OFF 时间不同时,我们可以将时钟信号表示为脉冲序列。下图显示了此时钟信号。

在上图中,脉冲序列被视为时钟信号。此信号在一段时间内保持逻辑高电平(5V),在另一段时间内保持逻辑低电平(0V)。此模式在一段时间内重复。在这种情况下,时间周期将等于 ON 时间和 OFF 时间的总和。

时钟信号时间周期的倒数称为时钟信号的频率。所有时序电路都使用时钟信号进行操作。因此,必须根据时钟信号频率选择时序电路的运行频率。

触发类型

以下是时序电路中使用的两种可能触发类型。

- 电平触发

- 边沿触发

电平触发

时钟信号有两种电平,即逻辑高电平和逻辑低电平。以下是两种电平触发类型。

- 正电平触发

- 负电平触发

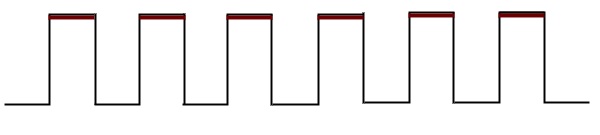

如果时序电路在时钟信号处于逻辑高电平时运行,则该触发类型称为正电平触发。下图中突出显示。

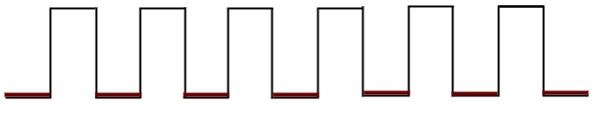

如果时序电路在时钟信号处于逻辑低时使用时钟信号运行,则该类型的触发称为负电平触发。下图中突出显示。

边沿触发

时钟信号中发生两种类型的转换。这意味着,时钟信号从逻辑低电平转换为逻辑高电平或从逻辑高电平转换为逻辑低电平。

以下是基于时钟信号转换的两种边沿触发类型。

- 正边沿触发

- 负边沿触发

正边沿触发

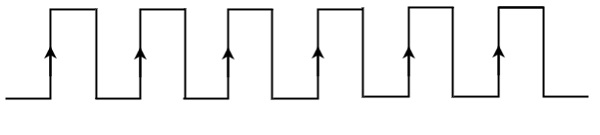

如果时序电路使用从逻辑低电平转换为逻辑高电平的时钟信号运行,则该类型的触发称为正边沿触发。它也被称为上升沿触发。如下图所示。

负边沿触发

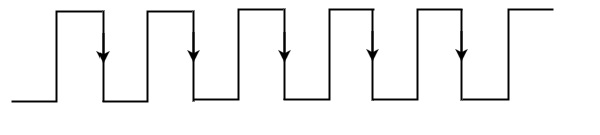

如果时序电路使用从逻辑高电平转换为逻辑低电平的时钟信号,则该类型的触发称为负边沿触发。它也被称为下降沿触发。如下图所示。

在接下来的章节中,我们将根据可用于其中的触发类型讨论各种时序电路。