时钟控制 JK 触发器

在数字电子技术中,触发器是用于存储 1 位信息的多种电子电路中最基本的存储元件。触发器基本上是一种具有两个稳定状态的双稳态多谐振荡器。

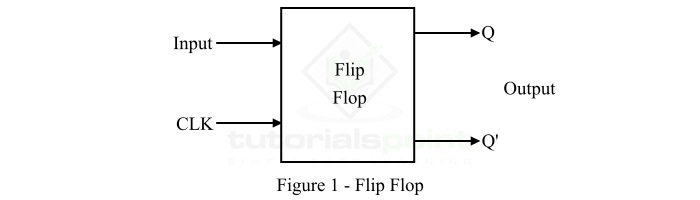

触发器由逻辑门组合而成。但是,逻辑门本身无法存储信息,但当多个逻辑门以特定方式连接时,它们可以存储信息。此外,触发器是所有顺序逻辑电路的最基本构建块。图 1 显示了触发器的框图。

触发器有一个或多个输入和两个输出,通常用 Q 和 Q' 表示,还有一个时钟输入。时钟输入用于触发触发器,以便它可以改变其输出的状态。

触发器有多种类型,例如SR 触发器、JK 触发器、D 触发器和T 触发器。每种类型的触发器都有其独特的属性和特性,以满足特定目的。

本文旨在解释时钟 JK 触发器的电路图、真值表和布尔表达式。因此,让我们从时钟 JK 触发器的基本介绍开始。

什么是时钟 JK 触发器?

具有两个分别由字母 J 和 K 指定的输入的触发器称为JK 触发器。对于 JK 触发器,符号 J 和 K 与 SR 触发器中的字母 S 和 R 相似。

从技术上讲,JK 触发器基本上是 SR 触发器的改进,其中定义了 SR 触发器的无效或禁止状态。

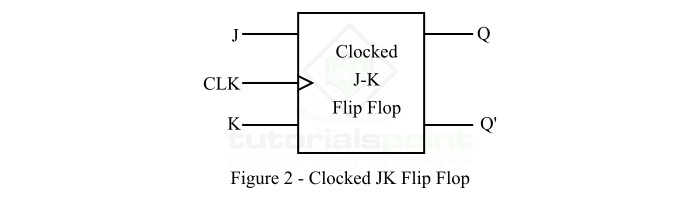

JK 触发器的框图表示如下图 2 所示。

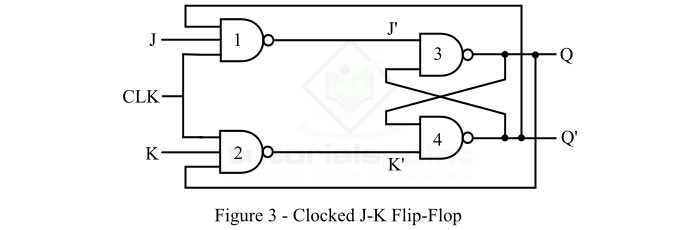

JK 触发器的逻辑电路图如图 3 所示。

因此,JK触发器有两个输入端,标记为 J 和 K,以及两个输出端,标记为 Q 和 Q'。它还有一个额外的时钟信号输入端。时钟信号用于同步触发器电路。

JK触发器以发明家杰克·基尔比(Jack Kilby)的名字命名为"JK",他于1958年发明了集成电路(IC)。

时钟控制JK触发器的操作

上述时钟控制JK触发器电路的操作如下所述−

当时钟信号不存在时,电路将保持不活动状态,并且NAND门3和4的输出不会随着输入J和K的任何变化而变化。

当时钟信号施加到电路时,NAND门3和4的输出将与输入J和K一致。在这种情况下,电路将按照以下真值表所述运行-

| 输入 | 上一个状态 | 输出 | (下一个状态) | 注释 |

|---|---|---|---|---|

| J | K | Qn | Qn+1 | |

| 0 | 0 | 0 | 0 | No Change |

| 0 | 0 | 1 | 1 | No Change |

| 0 | 1 | 0 | 0 | Reset |

| 0 | 1 | 1 | 0 | Reset |

| 1 | 0 | 0 | 1 | Set |

| 1 | 0 | 1 | 1 | Set |

| 1 | 1 | 0 | 1 | Toggle |

| 1 | 1 | 1 | 0 | Toggle |

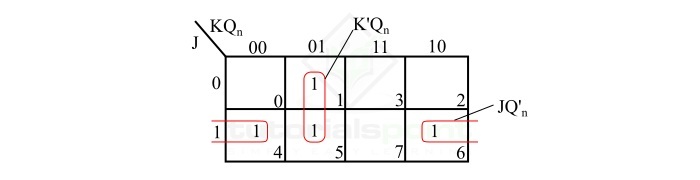

从时钟控制的 JK 触发器的真值表中,我们可以得出触发器的特征方程如下 −

因此,JK 触发器的特征方程为,

$$\mathrm{Q_{n+1}\:=\:JQ_{n}^{'}\:+\:K'Q_{n}}$$

时钟控制的 JK 触发器的优点

JK 触发器的主要优点如下 −

- 在 JK 触发器中,不会发生禁止状态。

- 在 JK 触发器中,禁止状态,当前状态切换,即当两个输入(J 和 K)均为 1 时,当前状态得到补充。

这就是数字电子器件中的时钟 JK 触发器的全部内容。