同步或时钟 S-R 触发器

在数字电子技术中,触发器 是最基本的存储元件,用于存储 1 位信息。触发器基本上是具有两个稳定状态的双稳态多谐振荡器。

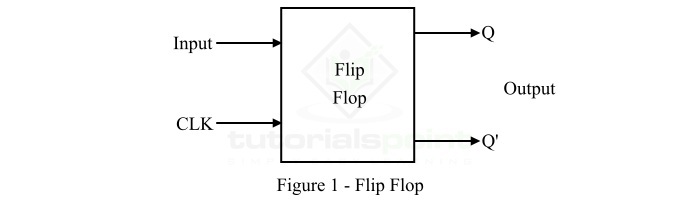

触发器由逻辑门互连而成。但是,逻辑门本身不具备存储能力,但当多个逻辑门以特定方式排列时,它们可以存储信息。此外,触发器是顺序逻辑电路最基本的构建块。图 1 显示了典型触发器的框图。

触发器有一个或多个输入和两个输出,通常用 Q 和 Q' 表示,还有一个时钟输入。时钟输入用于触发触发器,以便它可以改变其输出的状态。

有几种类型的触发器,例如SR 触发器、JK 触发器、D 触发器和T触发器。每种类型的触发器都有其独特的属性和特性,以满足特定目的。

同步和异步触发器

逻辑电路由时钟信号计时/触发的触发器称为同步触发器。因此,同步触发器的输出状态在没有时钟信号的情况下不会改变,即使其输入多次改变也是如此。

另一方面,异步触发器是没有时钟信号的触发器,因此其输出在输入应用时会立即改变。

现在,让我们详细讨论时钟或同步 S-R 触发器。

什么是时钟 SR 触发器?

具有两个输入(即 S(设置)和 R(重置))的触发器称为 SR 触发器。如果触发器的 S 和 R 输入在时钟脉冲存在时控制其输出(即从低到高或从高到低),则称为 时钟 SR 触发器。由于时钟信号同步 SR 触发器的操作,因此时钟 SR 触发器也称为同步 SR 触发器。时钟或同步 SR 触发器的框图如图 2 所示。

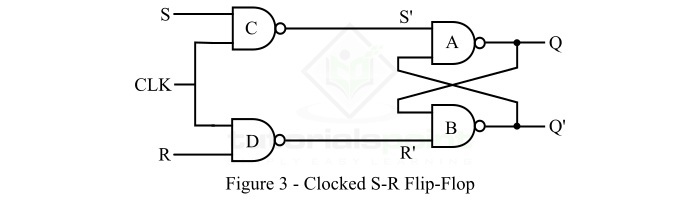

时钟或同步 SR 触发器的逻辑电路图如下图 3 所示。

可以看出,该电路由四个 NAND 门组成。时钟信号连接到 NAND 门 C 和 D,输入 S 和 R 也施加到 NAND 门 C 和 D。NAND 门 A 和 B 交叉耦合以形成触发器的存储电路。

时钟 SR 触发器的操作

此时钟 SR 触发器电路的操作如下所述 −

- 当未施加时钟信号时,SR 触发器电路保持不活动状态,触发器的输出没有变化。

- 当施加时钟信号时,触发器电路变为活动状态并按如下所述操作 −

- 当 S = 0 和 R = 0 时,NAND 门 C 和 D 的输出为 S' = 1 和 R' = 1。因此,NAND 门 A 和 B 的输出保持不变。这称为 SR 触发器的保持状态。

- 当 S = 0 且 R = 1 时,NAND 门 C 和 D 的输出为 S' = 1 和 R' = 0,NAND 门 A 的输出为 0,NAND 门 B 的输出为 1。这称为 SR 触发器的复位状态。

- 当 S = 1 且 R = 0 时,NAND 门 C 和 D 的输出为 S' = 0 和 R' = 1,NAND 门 A 的输出为 1,NAND 门 B 的输出为 0。这称为 SR 触发器的设置状态。

- 当 S = 1 且 R = 1 时,NAND 门 C 和 D 的输出为 S' = 0 和 R' = 0,NAND 门 A 和 B 的输出都试图变为1,这是不可能的。这被称为 SR 触发器的禁止状态。

时钟控制 SR 触发器的真值表

我们还可以用真值表的形式来表示时钟控制 SR 触发器的操作,如下所示。这里,S 和 R 指定输入,Qn 指定输出的当前状态,Qn+1 指定输入改变和施加时钟脉冲后输出的状态。

| 输入 | 输出 | 注释 | ||

|---|---|---|---|---|

| S | R | Qn | Qn+1 | |

| 0 | 0 | 0 | 0 | 无变化/持有 |

| 0 | 0 | 1 | 1 | 无变化/持有 |

| 0 | 1 | 0 | 0 | 重置 |

| 0 | 1 | 1 | 0 | 重置 |

| 1 | 0 | 0 | 1 | 设置 |

| 1 | 0 | 1 | 1 | 设置 |

| 1 | 1 | 0 | X | 禁止 |

| 1 | 1 | X | 禁止 | |

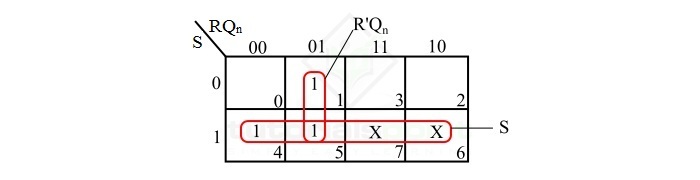

从这个时钟 SR 触发器的真值表中,我们可以直接为其输出 Qn+1 写出布尔表达式,如下所示 −

因此,SR 触发器的特性方程为,

$$\mathrm{Q_{n+1}\:=\:S\:+\:R'Q_{n}}$$

时钟控制 SR 触发器的应用

时钟控制 SR 触发器用于以下应用 −

- 数字计数器

- 存储和移位寄存器

- 数据存储元件

- 数据传输系统

- 分频器电路等

结论

时钟控制 SR触发器是一种顺序逻辑电路,在数字系统中用作 1 位存储设备。它有两个输入 S(设置)和 R(复位)。当 R 为高电平时,SR 触发器处于复位状态;当 S 为高电平时,SR 触发器处于设置状态;当 S 和 R 输入都为高电平时,SR 触发器处于禁止或无效状态;当 S 和 R 输入都为低电平时,SR 触发器处于不变或保持状态。