二进制加法器 - 减法器

二进制加法器-减法器是一种数字电路,用于执行两种基本算术运算,即二进制加法和二进制减法。它是计算机、计算器等各种数字系统中的重要组成部分。

使用二进制加减器的最显著优点是它将加法和减法运算结合在一个电路中,从而减小了体积并降低了成本。

阅读本章以了解二进制加减器的电路和操作。

什么是二进制加减器?

在数字电子技术中,有一种用于执行加法和减法运算的数字电路,称为二进制加减器。

二进制加减器是一种专门设计的数字算术电路,它将二进制数的加法和减法功能结合在一个电路中。

二进制加减器电路按照以下规则对两个二进制数执行二进制加法和减法运算。

二进制规则加法

执行二进制加法 − 时应遵循以下规则

| 第一位 (A) | 第二位 (B) | 和 (A + B) | 进位 |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

二进制减法规则

下表显示了执行二进制减法时应遵循的规则 −

| First Bit (A) | Second Bit (B) | Sum (A - B) | Borrow |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

以上就是二进制加减器的基本介绍以及二进制加法和减法的规则。现在让我们了解二进制加减器的电路结构。

二进制加减器电路

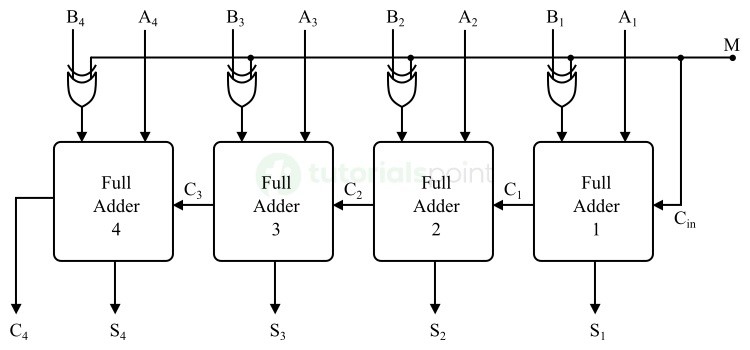

二进制加减器的逻辑电路由多个连接在一起的全加器电路组成。它还由一个由异或门组成的控制电路组成,并执行模式选择功能,即控制电路用于在加法和减法之间切换电路操作。

可以执行两个 4 位二进制数(例如 A 和 B)的加法或减法的二进制加法器-减法器的电路图如下所示 −

二进制加法器-减法器的组件

二进制加法器-减法器的电路由以下主要组件组成 −

全加器

全加器是一种二进制算术电路,用于一次执行三个二进制位的加法。它产生两个输出,即总和和进位。在二进制加法器-减法器电路中,全加器电路还可以使用补码机制执行减法运算。

控制电路

它是用于模式选择的逻辑电路,即加法模式或减法模式。二进制加法器-减法器的控制电路是使用 XOR 门设计的。

二进制加法器-减法器的工作原理

现在让我们了解上图所示的二进制加法器-减法器电路的操作。

上图所示的电路是一个 4 位二进制加法器-减法器。因此,它可以对两个 4 位二进制数(例如 A 和 B)进行加法或减法。

在此电路中,输入 M 称为模式输入。它控制电路的操作,如下所述 −

- 当 M = 0 时,电路作为二进制加法器运行。在此模式下,我们得到 $\mathrm{B_{X} \: \oplus \: 0 \: = \: B_{X}}$。因此,每个全加器接收输入 Ax 和 Bx 并执行它们的加法,即 Ax + Bx。

- 当 M = 1 时,电路作为二进制减法器运行。在这种情况下,我们得到 $\mathrm{B_{X} \: \oplus \: 1 \: = \: B_{X}}$' 且输入进位 Cin = 1。在这种模式下,全加器以互补形式接收 Bx 输入,并通过输入进位 Cin 添加 1。因此,电路的最终输出是 Ax + Bx 的 2 的补码,即 Ax 和 Bx 的减法。

这就是二进制加法器-减法器电路执行二进制加法和二进制减法运算的方式。

我们可以从以下几点总结二进制加法器-减法器的工作原理 −

- 首先,选择电路的操作模式(加法或减法)。要执行二进制加法,请设置 M = 0;要执行二进制减法,请设置 M = 1。

- 提供要相加或相减的两个输入二进制数。

- 电路将根据所选模式对输入数字执行加法或减法,并产生结果(总和或差值)。

二进制加法器-减法器的优点

在数字电路设计领域,尽可能使电路紧凑非常重要。由于二进制加法器-减法器电路将二进制加法和减法运算结合在一个电路中。它具有以下主要优势 −

- 降低电路复杂性

- 紧凑、更简单的系统设计

- 多功能性

- 能够执行快速、高效的算术运算

- 减少对硬件组件的需求

- 与各种数字系统和设备兼容

- 低功耗等

二进制加法器-减法器的局限性

二进制加法器-减法器具有上述几个优点。但它也有一些缺点和局限性。

二进制加法器-减法器的一些关键限制如下所列−

- 二进制加法器-减法器需要更先进的电路元件和算法才能在加法和减法运算中实现高精度和准确度。

- 二进制加法器-减法器的功能仅限于加法和减法运算。它需要额外的电路和算法来实现其他数学运算,如乘法和除法。

- 当二进制加法器-减法器被设计用于执行大量位和浮点数的加法和减法时,其电路复杂性会显著增加。

- 当要加或减的数字的位数增加时,由于传播延迟,电路会变慢。

- 二进制加法器-减法器的动态范围有限,因此在处理非常大或非常小的数字时可能会发生溢出或下溢情况。

- 由于二进制加法器-减法器使用2的补码算法来执行二进制减法。为了实现此操作,我们需要一个额外的逻辑电路,这会增加电路的整体复杂性。

在设计二进制加法器-减法器时,我们必须考虑所有这些限制,以确保电路具有更高的效率和更好的性能。

二进制加法器-减法器的应用

在数字电子技术中,二进制加法器-减法器可用于各种数字系统和电子设备。下面列出了一些常见的设备,其中二进制加法器-减法器是关键组件 −

- 算术逻辑单元 − 执行算术和逻辑运算。

- 微处理器和微控制器 − 执行数学计算。

- 通信系统 −处理数字信号并对二进制数据进行过滤操作。

- 计算器 − 执行加法和减法运算。

- 控制系统 − 执行实时信号处理并产生反馈和其他控制信号。

结论

在本章中,我们解释了二进制加法器-减法器的基本理论和工作原理。二进制加法器-减法器是一种可以执行二进制数加法和减法的数字电子电路。它将两个算术运算(加法和减法)组合成一个电路,从而降低了数字系统的电路复杂性和尺寸。

二进制加法器-减法器广泛应用于各种数字系统和设备,如微处理器、微控制器、计算器等。