CPU 架构

微处理单元与中央处理单元、传统计算机中使用的 CPU 同义。微处理器 (MPU) 充当执行以下任务的设备或一组设备。

- 与外围设备通信

- 提供定时信号

- 直接数据流

- 按照内存中的指令执行计算机任务

8085 微处理器

8085 微处理器是一种 8 位通用微处理器,能够寻址 64k 内存。该处理器有四十个引脚,需要 +5 V 单电源和 3 MHz 单相时钟。

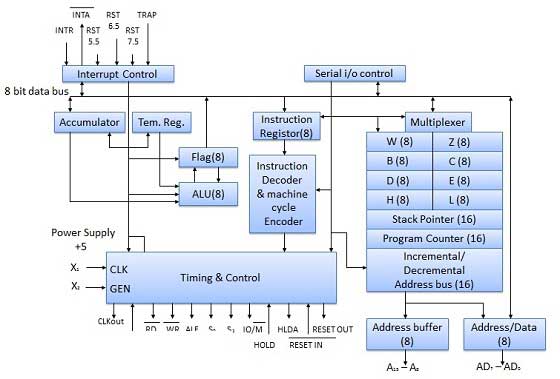

框图

ALU

ALU 执行微处理器的计算功能。它包括累加器、临时寄存器、算术和逻辑电路以及五个标志。结果存储在累加器和标志中。

框图

累加器

它是一个 8 位寄存器,是 ALU 的一部分。此寄存器用于存储 8 位数据并执行算术和逻辑运算。运算结果存储在累加器中。

图表

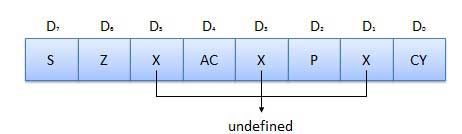

标志

标志是可编程的。它们可用于使用指令存储和传输来自寄存器的数据。ALU 包括五个触发器,它们根据累加器和其他寄存器中的数据条件进行设置和重置。

- S(符号)标志 − 执行算术运算后,如果结果的位 D7 为 1,则设置符号标志。它用于有符号数。在给定字节中,如果 D7 为 1,则表示负数。如果为零,则表示为正数。

- Z(零)标志 − 如果 ALU 操作结果为 0,则设置零标志。

- AC(辅助进位)标志 − 在算术运算中,当数字 D3 生成进位并传递给数字 D4 时,会设置 AC 标志。此标志仅在 BCD 操作内部使用。

- P(奇偶校验)标志 − 算术或逻辑运算后,如果结果中有偶数个 1,则设置该标志。如果有奇数个 1,则重置标志。

- C(进位)标志 −如果算术运算结果为进位,则设置进位标志,否则重置。

寄存器部分

它基本上是一个存储设备,使用指令从寄存器传输数据。

- 堆栈指针 (SP) − 堆栈指针也是一个 16 位寄存器,用作内存指针。它指向读/写内存中称为堆栈的内存位置。在程序执行期间,有时数据要存储在堆栈中。堆栈的开头通过在堆栈指针中加载 16 位地址来定义。

- 程序计数器 (PC) − 这个 16 位寄存器处理第四个操作以对指令的执行进行排序。该寄存器也是一个内存指针。内存位置有 16 位地址。它用于存储执行地址。程序计数器的功能是指向下一个字节要从中获取的内存地址。

- 存储寄存器 − 这些寄存器在程序执行期间存储 8 位数据。这些寄存器被标识为 B、C、D、E、H、L。它们可以组合成寄存器对 BC、DE 和 HL,以执行一些 16 位操作。

时间和控制部分

该单元负责根据时钟脉冲同步微处理器操作,并生成微处理器与外围设备之间顺利通信所需的控制信号。RD 条和 WR 条信号是同步脉冲,指示数据总线上是否有数据。控制单元负责控制微处理器、内存和外围设备之间的数据流。

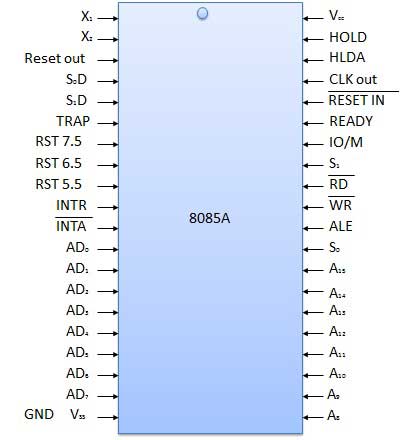

PIN 图

所有信号可分为六组

| Sr.No | 组 | 描述 |

|---|---|---|

| 1 | 地址总线 | 8085 微处理器有 8 条信号线,A15 - A8 是单向的,用作高位地址总线。 |

| 2 | 数据总线 | 信号线 AD7 - AD0 是双向的,用于双重用途。它们既用作低位地址总线,又用作数据总线。 |

| 3 | 控制信号和状态信号 |

控制信号 RD bar − 它是一个读取控制信号(低电平有效)。如果它处于活动状态,则内存读取数据。 WR bar − 它是写入控制信号(低电平有效)。当写入选定的内存时,它处于活动状态。 状态信号 ALE(地址锁存启用) − 当 ALE 为高电平时。8085 微处理器使用地址总线。当 ALE 为低电平时。8085 微处理器使用数据总线。 IO/M bar −这是用来区分I/O和内存操作的状态信号,高电平表示I/O操作,低电平表示内存操作。 S1和S0 − 这些状态信号与I/O和内存条类似,可以识别各种操作,但在小型系统中很少使用。 |

| 4 | 电源和频率信号 |

Vcc − +5v电源。 Vss − 接地参考。 X, X − 这两个引脚上连接有晶体。频率在内部被两个操作系统分频为 3 MHz,晶体的频率应为 6 MHz。 CLK 输出 − 此信号可用作其他设备的系统时钟。 |

| 5 | 外部发起信号 |

INTR (i/p) − 中断请求。 INTA bar (o/p) − 它用作确认中断。 TRAP (i/p) − 这是不可屏蔽中断,具有最高优先级。 HOLD (i/p) −它用于保持正在执行的程序。 HLDA (o/p) − 保持确认。 READY (i/p) − 此信号用于延迟微处理器读取或写入周期,直到响应缓慢的外围设备准备好接受或发送数据。 RESET IN bar − 当此引脚上的信号变为低电平时,程序计数器设置为零,总线为三态,并且 MPU 复位。 RESET OUT − 此信号表示 MPU 正在复位。该信号可用于复位其他设备。 RST 7.5、RST 6.5、RST 5.5(请求中断) − 它用于将程序控制转移到特定的内存位置。它们的优先级高于 INTR 中断。 |

| 6 | 串行 I/O 端口 | 8085 微处理器有两个信号用于实现串行传输串行输入数据和串行输出数据。 |

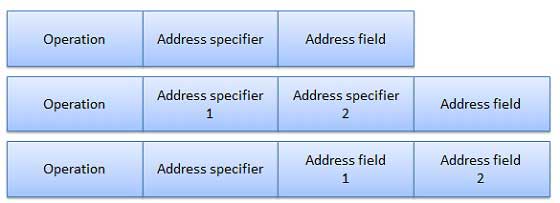

指令格式

每条指令都由计算机内的一系列位表示。指令被分成称为字段的位组。指令的表达方式称为指令格式。它通常以矩形框的形式表示。指令格式可能属于以下类型。

可变指令格式

这些是指令格式,其中指令长度根据操作码和地址说明符而变化。例如,VAX 指令在 1 到 53 个字节之间变化,而 X86 指令在 1 到 17 个字节之间变化。

格式

优点

这些格式具有良好的代码密度。

缺点

这些指令格式很难解码和流水线化。

固定指令格式

在这种类型的指令格式中,所有指令的大小相同。例如,MIPS、Power PC、Alpha、ARM。

格式

优点

它们易于解码和流水线化。

缺点

它们没有良好的代码密度。

混合指令格式

在这种类型的指令格式中,我们有多个由操作码指定的格式长度。例如,IBM 360/70、MIPS 16、Thumb。

格式

优点

这些代码密度和此类指令之间的折衷非常容易解码。

寻址模式

寻址模式为处理器提供了访问给定数据地址的不同方式。操作数据存储在内存位置,每条指令都需要对其进行操作的特定数据。有多种技术可以指定数据的地址。这些技术称为寻址模式。

- 直接寻址模式 −在直接寻址模式下,操作数的地址在指令中给出,数据在指令提供的内存位置中可用。我们将把这些数据移动到所需的位置。

- 间接寻址模式 − 在间接寻址模式下,指令指定一个包含操作数地址的寄存器。内部 RAM 和外部 RAM 都可以通过间接寻址模式访问。

- 立即寻址模式 − 在立即寻址模式下,直接数据在操作数中给出,该操作数将数据移动到累加器中。它非常快。

- 相对寻址模式 − 在相对地址模式下,有效地址由索引模式确定,使用程序计数器而不是通用处理器寄存器。此模式称为相对地址模式。

- 索引寻址模式 −索引寻址模式中,操作数的有效地址由寄存器内容加上内容值生成,这种模式称为索引寻址模式。