数字电子技术 - 组合电路

组合电路,也称为组合逻辑电路,是一种数字电子电路,其输出仅由当前输入决定。

组合逻辑电路的输出不依赖于电路操作的历史。换句话说,组合电路是一种数字逻辑电路,其输出仅取决于当前输入值,而不依赖于任何反馈或先前的输入或输出值。

在本章中,我们将解释组合电路的基础知识及其框图、类型和应用。那么,让我们从组合电路的基本定义开始。

什么是组合电路?

组合电路是一种数字逻辑电路,其输出仅取决于当前输入值,而不依赖于过去的输入和输出值。因此,组合电路被认为在其电路中没有存储先前输入和输出的存储元件。相反,它由一定数量的输入线组成以应用当前输入值,并由一定数量的输出线组成。

组合电路最重要的特征是它在输入和输出之间没有任何反馈路径。因此,组合电路可以归类为开环系统。

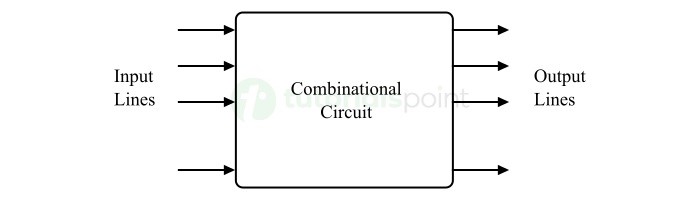

组合电路的框图

下图描绘了组合逻辑电路的框图。

在这里,我们可以看到组合电路的电路图中只有三个关键元素,它们是 −

- 输入线 −输入线用于将输入值输入到组合电路中。

- 处理单元 − 它是根据电路类型处理输入值的主要元件。例如,全加器将三个二进制位相加。

- 输出线 − 输出线用于获取电路生成的结果。

组合电路的特性

以下是组合电路的主要特性 −

- 组合电路的输出在任何时刻仅取决于该时刻的当前输入值。

- 组合电路在其电路中不使用任何类型的存储元件。因此,输入和输出值的先前状态对电路的当前操作没有任何影响。

- 可以使用组合电路的逻辑运算和输入值完全预测其输出。

- 组合电路会响应其输入值的任何变化而产生瞬时输出。

组合电路的类型

在数字电子技术中,组合电路是数字系统的重要组成部分。根据所执行的功能,组合电路有多种类型。下面解释了一些常见的组合电路类型及其功能 −

- 二进制加法器

- 二进制减法器

- 多路复用器 (MUX)

- 多路分解器 (DEMUX)

- 编码器

- 解码器

- 比较器

在本章的以下部分中,我们将简要讨论这些组合电路及其功能。

二进制加法器

二进制加法器是一种执行二进制数字或位加法的组合电路。根据设计和配置,二进制加法器有两种类型,即半加法器和全加法器。

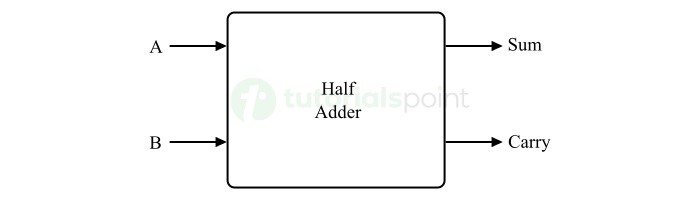

半加法器

半加法器是一种具有两个输入和两个输出的组合逻辑电路。半加法器电路用于将两个单比特二进制数 A 和 B 相加。它是两个单比特数相加的基本构建块。该电路有两个输出,即和和进位。

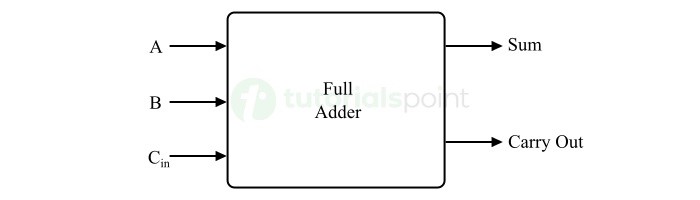

全加器

全加器旨在克服半加器的缺点,即只能加两位。因此,全加器是一个三输入和两输出的组合电路。其中,输入是两个一位数 A 和 B,以及来自前一次加法的进位 C。输出是总和和进位输出。

二进制减法器

二进制减法器是一种组合逻辑电路,用于将一个二进制数减去另一个二进制数。与二进制加法器类似,二进制减法器也有两种类型,即半减法器和全减法器。

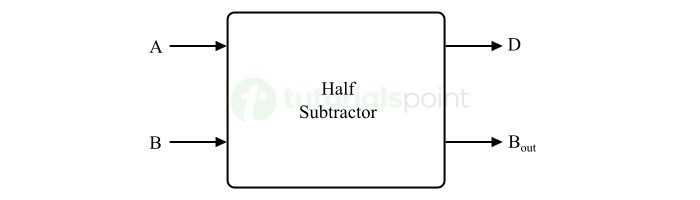

半减法器

半减法器 是一个具有两个输入(A 和 B)和两个输出(差和借位)的组合电路。它产生输入端两个二进制位之间的差值,并产生一个输出(借位)来指示是否已借位 1。在二进制减法 (A-B) 中,A 称为被减数位,B 称为减数位。

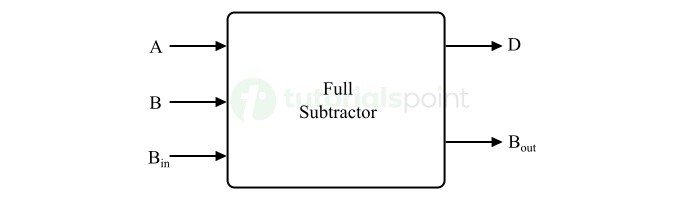

全减器

全减器 也是一个组合电路,有三个输入 A、B 和 Bin,以及两个输出 D 和 Bout。

这里,A 是被减数位,B 是减数位,Bin 是前一级产生的前一个借位,D 是差值输出,Bout 是借位输出。

多路复用器 (MUX)

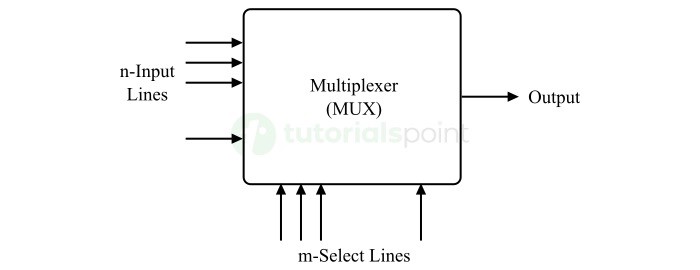

多路复用器是一种特殊类型的组合逻辑电路。它由 n 条数据输入线、一个输出和 m 条选择线组成。对于多路复用器,n = 2m。

多路复用器是一种数字电路,它选择 n 个数据输入中的一个并将其路由到输出线。n 个数据输入中的一个的选择由选择线完成。根据选择线上应用的数字代码,从"n"个数据输入中选择一个并将其传输到输出线。

在某些多路复用器中,还有一个启用输入 E,它在级联多个多路复用器时很有用。

根据输入线的数量,可以有几种类型的多路复用器。一些常见的多路复用器类型包括 2:1 多路复用器、4:1 多路复用器、16:1 多路复用器和 32:1 多路复用器。

多路分解器 (DEMUX)

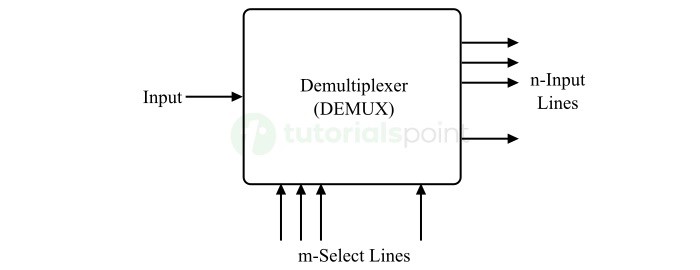

多路分解器执行分配操作,即,它接收一个数据输入并将其分配到多条输出线上。

多路分解器只有一条输入线、"n"条输出线和"m"条选择线。一次,仅通过应用于选择线的数字代码选择一条输出线,并将数据输入传输到选定的输出线。

多路分解器可根据输出线的数量分为各种类型。一些常用的解复用器类型包括:1:2 解复用器、1:4 解复用器、1:16 解复用器和 1:32 解复用器。

编码器

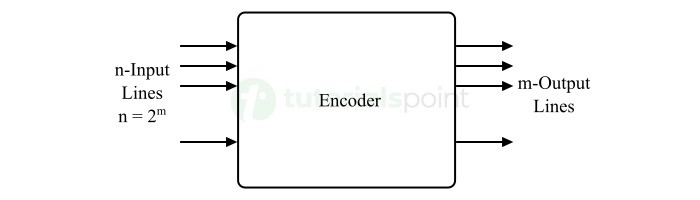

编码器是一种组合电路,旨在将一段信息转换为二进制代码。编码器有 n 条输入线和 m 条输出线,其中 n = 2m。

编码器生成与施加到它的数字输入相对应的 m 位二进制代码。换句话说,编码器接受 n 个输入数字字并将其转换为 m 位另一个数字字。

编码器的示例包括 4 转 2 编码器、八进制转二进制编码器、十六进制转二进制编码器、优先级编码器等。

解码器

解码器是一种组合电路,可将二进制代码转换为十进制数字等普通字。解码器通常由 n 条输入线和 m 条输出线组成,其中 m = 2n。

解码器广泛用于显示驱动器、数据分配系统等。

一些常用的解码器类型包括 2 到 4 解码器、3 到 8 解码器、4 到 16 解码器、BCD 到七段解码器等。

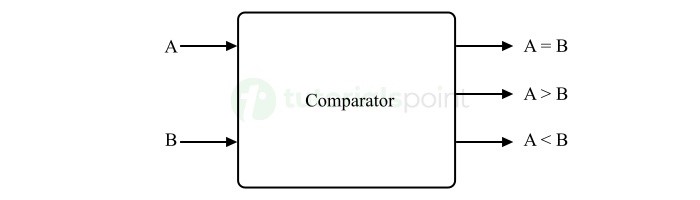

比较器

比较器是一种组合逻辑电路,用于比较两个二进制数。比较器主要用于算术和控制电路中,执行比较或逻辑运算。

顾名思义,比较器比较输入值并检查它们是否相等或一个输入大于/小于另一个输入。

组合电路的局限性

组合电路具有运算速度快、电路简单、操作可预测等优点。但是,它们也有几个局限性,其中一些列在下面 −

- 组合电路没有任何记忆元件。它们无法存储电路操作的历史记录。

- 组合电路不能用于实现某些高度复杂的逻辑功能。

- 组合电路没有任何反馈机制。这使得组合电路的功能有限。

- 从大尺度上讲,组合电路具有多种设计复杂性,可能导致性能不佳和资源利用效率低下。

组合电路的应用

组合电路是各种数字设备和系统的基本构件。它们广泛用于使用组合电路的多种数字设备中 −

- 微处理器和微控制器

- 数字计算机

- 计算器

- 数字通信系统

- 键盘

- 智能手机和数字手表等

结论

组合逻辑电路是各种数字设备和系统中的关键组件。它可以定义为数字组件的互连系统,其输出仅取决于输入的当前状态,而不取决于过去的输入和输出值。

在本章中,我们解释了组合电路的特点、局限性和应用。