可编程逻辑器件

可编程逻辑器件 (PLD) 是配置为执行各种逻辑功能的集成电路的集合。PLD 在工程和技术领域发挥着重要作用,因为它们构成了创新的基础,并支持工程师开发自动化数字系统以提高流程灵活性和效率。这里的"可编程"是指定义一个无需人工干预即可多次执行的功能。

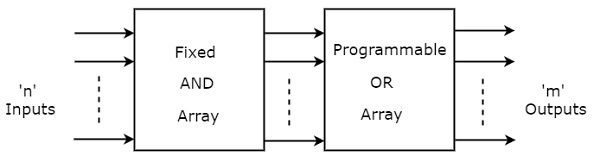

可编程逻辑器件(PLD) 是集成电路。它们包含一组与门阵列和另一组或门阵列。根据具有可编程功能的阵列类型,PLD 有三种类型。

- 可编程只读存储器

- 可编程阵列逻辑

- 可编程逻辑阵列

将信息输入这些设备的过程称为编程。基本上,用户可以对这些设备或 IC 进行电气编程,以便根据要求实现布尔函数。这里的编程一词指的是硬件编程,而不是软件编程。

在本章中,我们将解释可编程逻辑设备的基本概念、它们的类型、优点、局限性和应用。

可编程只读存储器 (PROM)

只读存储器 (ROM) 是一种存储设备,它永久存储二进制信息。这意味着,我们以后无法以任何方式更改存储的信息。如果 ROM 具有可编程功能,则称为可编程 ROM (PROM)。用户可以灵活地使用 PROM 编程器对二进制信息进行一次电气编程。

PROM 是一种可编程逻辑设备,具有固定的 AND 阵列和可编程的 OR 阵列。下图显示了 PROM 的框图。

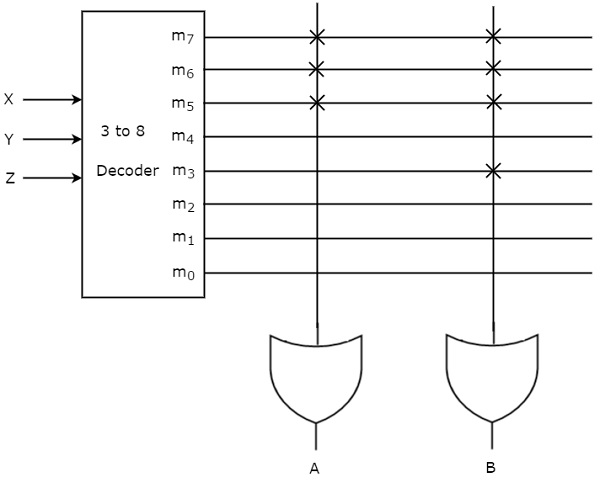

这里,AND 门的输入不是可编程类型。因此,我们必须使用每个具有 n 个输入的 2n AND 门来生成 2n 个乘积项。我们可以使用 nx2n 解码器来实现这些乘积项。因此,该解码器生成'n'个最小项。

此处,或门的输入是可编程的。这意味着,我们可以对任意数量的所需乘积项进行编程,因为与门的所有输出都作为每个或门的输入。因此,PROM 的输出将采用最小项之和的形式。

示例

让我们使用 PROM 实现以下布尔函数。

$$\mathrm{A(X,Y,Z)\:=\:\sum m\left ( 5,6,7 ight )}$$

$$\mathrm{B(X,Y,Z)\:=\:\sum m\left ( 3,5,6,7 ight )}$$

给定的两个函数采用最小项之和的形式,每个函数都有三个变量 X、Y 和 Z。因此,我们需要一个 3 到 8 解码器和两个可编程或门来生成这两个函数。相应的 PROM 如下图所示。

这里,3 到 8 解码器生成八个最小项。两个可编程或门可以访问所有这些最小项。但是,只有所需的最小项被编程,才能通过每个或门产生相应的布尔函数。符号"X"用于可编程连接。

什么是可编程逻辑器件?

可编程逻辑器件 (PLD) 可以定义为可编程执行特定功能的集成电路 (IC)。在这里,编程意味着我们可以定义一组指令,这些指令可以多次执行以执行功能,而无需任何人工干预。

开发 PLD 的主要需求是实现数字逻辑功能,这些功能可以复制传统逻辑电路的行为并多次复制。然而,PLD 在可编程性方面与普通数字逻辑电路不同,这意味着我们可以通过在设备中设置一组指令来定义所需的逻辑功能。

PLD 的类型

根据所用设备的类型,可编程逻辑设备 (PLD) 可分为以下两种类型 −

- 双极 PLD

- CMOS PLD

让我们详细讨论每种类型的可编程逻辑器件。

双极 PLD

双极 PLD 是一种可编程逻辑器件,其中双极结型晶体管 (BJT) 是主要功能器件。双极 PLD 是可编程逻辑器件的旧版本。因此,在 CMOS PLD 开发之前,它们就被广泛使用。

以下是双极可编程逻辑器件的一些重要特性 −

- 双极 PLD 提供快速的切换速度,因此它们可以在更高的频率下工作。

- 双极 PLD 更适合涉及快速信号处理并需要快速响应时间的应用。

- 双极 PLD 需要更多的功率才能运行。

- 双极 PLD 对电子噪声和干扰具有更好的免疫力。

所有这些特性使双极可编程逻辑器件非常适合用于高速运行和可靠性至关重要的应用,例如航空航天、军事和电信系统。

CMOS PLD

CMOS PLD 代表互补金属氧化物半导体可编程逻辑器件。顾名思义,CMOS PLD 使用 CMOS 晶体管,即 NMOS(N 沟道金属氧化物半导体)和 PMOS(P 沟道金属氧化物半导体)晶体管作为基本组件。

CMOS PLD 基本上是 PLD 的现代版本,由于其众多优点,在现代数字系统中得到广泛应用。

下面介绍了 CMOS PLD 的一些重要特性 −

- CMOS PLD 运行时所需的电量非常少。因此,这一特性使 CMOS PLD 非常适合用于电池供电设备,因为能源效率是其中的一个重要因素。

- CMOS PLD 更可靠、更耐用。因为它们的设计可以抵御各种环境因素,如高/低温、电压波动和不同的辐射干扰。

- CMOS PLD 在可扩展性方面也非常出色。

CMOS PLD 是较新的 PLD 设备,因此在各种现代电子设备中非常常用,如消费电子产品、医疗设备、工业自动化系统、汽车系统。

PLD 编程语言

对于可编程逻辑器件 (PLD),可以使用几种不同类型的硬件描述语言 (HDL) 对其进行编程。使用这些 PLD 编程语言,工程师和设计人员可以定义 PLD 电路的行为和逻辑功能。

这里介绍了一些最常用的 PLD 编程语言 −

VHDL

VHDL 代表 VHSIC 硬件描述语言。它是一种标准化的硬件描述语言,用于对数字电路和系统进行建模和仿真。使用 VHDL,工程师和开发人员可以指定数字电路的结构和功能。VHDL 是最适合组合电路和顺序电路的编程语言,因为它支持并发和顺序描述。

VHDL 是设计和验证高度复杂的数字电路和系统(如 PLD、ASIC、FPGA 等)的最广泛使用的编程语言之一。

Verilog

Verilog 也是一种硬件描述语言 (HDL),用于设计和编程 PLD。与 VHDL 类似,Verilog 也支持并发和顺序描述,使工程师和设计人员能够定义数字电路的结构和行为。

这种编程语言最常用于半导体行业,用于设计和编程不同类型的数字系统。

PALASM

PALASM 代表可编程阵列逻辑汇编器。它是另一种用于编程可编程逻辑设备 (PLD) 的硬件描述语言 (HDL) 和汇编器。在 PALASM 的情况下,PLD 的行为、逻辑功能和结构使用文本语言格式描述。因此,开发人员必须编写 PALASM 代码来描述所需的逻辑功能和互连。之后,这些代码被组装成适合可编程逻辑器件的格式。

然而,PALASM 是一种较旧的硬件描述语言,在 20 世纪 80 年代和 90 年代初期非常常用,用于开发基于 PLD 的逻辑电路。

ABEL

ABEL 代表高级布尔表达式语言。它是一种为编程可编程逻辑设备 (PLD) 而开发的高级硬件描述语言。

在 ABEL 中,逻辑方程、真值表和寄存器传输级设计描述使用清晰易读的语法指定。然后,ABEL 编译器将所有这些设计描述转换为适合编程所需 PLD 的格式。ABEL 是 20 世纪 90 年代非常常用的用户友好型硬件描述语言。

CUPL

CUPL 代表通用可编程逻辑编译器。它是另一种硬件描述语言 (HDL) 和编译器,用于对不同类型的 PLD 进行编程。在这种编程语言中,逻辑函数、真值表和顺序逻辑指令以简单语法的形式指定。

这种 HDL 语言在 20 世纪 90 年代和 21 世纪初也非常流行,用于设计基于 PLD 的逻辑电路。

所有这些都是用于设计和编程可编程逻辑设备的一些重要编程语言。PALASM、ABEL 和 CUPL 语言主要用于低复杂度设备。而 VHDL 和 Verilog 用于编程现代高度复杂的 PLD。

可编程逻辑器件的优势

可编程逻辑器件 (PLD) 具有众多优势,使其成为数字系统设计领域的重要工具。这里列出了可编程逻辑器件的一些重要优点 −

- 可编程逻辑器件 (PLD) 易于编程和重新编程。因此,它们在设计和实现各种逻辑功能方面提供了极大的灵活性。

- PLD 允许设计定制逻辑电路以满足应用程序的特定要求。这可以通过对设备的内部逻辑电路进行编程来实现。

- PLD 可用于数字电路的原型设计和测试,这有助于以更快的速度开发新产品。通过加快产品开发过程,PLD 有助于减少硬件设计所需的时间和成本。

- PLD 提供了一种快速且经济高效的方法来开发中型到复杂的数字逻辑电路和系统。 PLD 通过将大量逻辑功能和组件集成到单个设备中,有助于开发简单、便宜且紧凑的数字系统。

- PLD 还支持并行处理、流水线处理等现代处理技术。此功能有助于通过同时执行逻辑功能实现高性能。

可编程逻辑器件的局限性

可编程逻辑器件 (PLD) 具有如上所述的几个优点,但它们也有一定的局限性。以下是可编程逻辑器件的一些主要局限性 −

- 可编程逻辑器件可以设计为支持有限数量的逻辑功能和元件。因此,复杂数字电路的实现可能需要多个器件。

- PLD 通常具有固定数量的输入/输出 (I/O) 引脚。这种限制可能会导致连接和与外部/外围设备接口方面的问题。

- 编程 PLD 需要了解硬件描述语言 (HDL) 和设计工具。有时 PLD 可能会因无意的重新编程或数据损坏而发生故障。

- PLD 本身不支持通用处理器中使用的复杂算术运算和其他高级编程操作。因此,开发人员必须通过自定义逻辑设计来实现此类操作和功能。

可编程逻辑器件的应用

可编程逻辑器件 (PLD) 广泛应用于不同领域和行业,用于设计数字逻辑电路和实现各种逻辑功能。下面列出了可编程逻辑器件的一些常见应用 −

- PLD 广泛用于嵌入式系统,以执行不同的实时操作,如控制、接口和数据处理。

- 在数字信号处理领域,PLD 用于设计数字滤波器、开发调制解调器算法、执行信号处理等。

- PLD 在通信系统中发挥着重要作用,因为它们有助于执行各种操作,如信号路由、数据加密和解密、协议转换等。

- 在航空航天和国防领域,PLD 用于完成各种关键功能,如飞行控制、操作雷达系统、引导导弹、加密机密数据等。

- PLD 还用于机器人和工业自动化,以控制和监控机械。

- 在医疗设备中,PLD 用于自动高速数据处理、医疗数据的实时分析、患者监测等。

结论

总之,可编程逻辑器件是一种可以编程或训练以执行特定逻辑功能的数字设备。它主要用于各种应用中的自动化和效率改进目的。

在本章中,我们解释了 PLD 的基础知识、类型、优点、局限性和应用。在下一章中,我们将探讨不同类型的可编程逻辑器件及其功能和特性。