数字算术电路

在本章中,我们将讨论二进制加法器和二进制减法器等基本算术电路。这些电路可以使用二进制值 0 和 1 进行操作。

二进制加法器

最基本的算术运算是加法。执行两个二进制数相加的电路称为二进制加法器。首先,让我们实现一个执行两位相加的加法器。

半加法器

半加法器是一种组合电路,执行两个单个位的二进制数 A 和 B 的加法。它产生两个输出和,S 和进位,C。

半加器的真值表如下所示。

| 输入 | 输出 | ||

|---|---|---|---|

| A | B | C | S |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

当我们将两位相加时,结果和的值在十进制中可以是 0 到 2 之间的值。我们可以用二进制中的单个位表示十进制数字 0 和 1。但是,我们不能用二进制中的单个位表示十进制数字 2。因此,我们需要两位来以二进制表示它。

假设和 S 是结果和的最低有效位,进位 C 是结果和的最高有效位。对于前三种输入组合,进位 C 为零,并且 S 的值将为零或一,具体取决于输入中存在的1 的数量。但是,对于最后一种输入组合,进位 C 为 1,和 S 为 0,因为结果和为 2。

从真值表,我们可以直接将每个输出的布尔函数写为

$$\mathrm{S \: = \: A \: \oplus \: B}$$

$$\mathrm{C \: = \: AB}$$

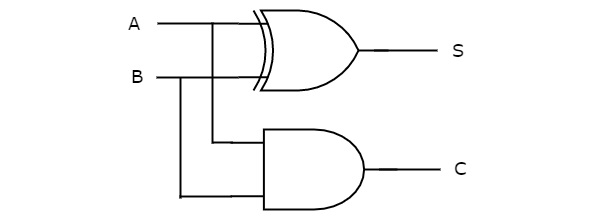

我们可以使用 2 输入异或门和 2 输入与门来实现上述函数。半加器的电路图如下图所示。

在上述电路中,两个输入异或门和两个输入与门分别产生和 S 和进位 C。因此,半加器执行两位的加法。

全加器

全加器是一个组合电路,它执行三个位A、B 和 Cin 的加法。其中,A 和 B 是两个并行的有效位,Cin 是进位位,由前一阶段生成。该全加器还产生两个输出和 S 和carry、Cout,与半加器类似。

全加器的真值表如下所示。

| 输入 | 输出 | |||

|---|---|---|---|---|

| A | B | Cin | Cout | S |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

当我们将三位相加时,结果和的十进制值范围为 0 到 3。我们可以用二进制中的单个位表示十进制数字 0 和 1。但是,我们不能用二进制中的单个位表示十进制数字 2 和 3。因此,我们需要两位来表示二进制中的这两个十进制数字。

假设,和,S 是最低有效位,进位,Cout 是结果和的最高有效位。在真值表中,很容易为所有输入组合填充输出值。只需计算输入中存在的1个数,并在输出中写入等效的二进制数。如果 Cin 等于零,则全加器真值表与半加器真值表相同。

简化后,我们将为每个输出获得以下布尔函数。

$$\mathrm{S \: = \: A \: \oplus \: B \: \oplus \: C_{in}}$$

$$\mathrm{c_{out} \: = \: AB \: + \: \left ( A \: \oplus \: B \right ) \: c_{in}}$$

当奇数个 1 时,总和 S 等于一输入。我们知道异或门产生的输出是奇函数。因此,我们可以使用两个 2 输入异或门或一个 3 输入异或门来产生和 S。我们可以使用两个 2 输入与门和一个或门来实现进位 Cout。全加器的电路图如下图所示。

此加法器称为全加器,因为要实现一个全加器,我们需要两个半加器和一个或门。如果 Cin 为零,则全加器变为半加器。我们可以从上面的电路图或全加器输出的布尔函数中轻松验证这一点。

4 位二进制加法器

4 位二进制加法器执行两个 4 位数的加法。设 4 位二进制数为 $\mathrm{A \: = \: A_{3}A_{2}A_{1}A_{0}}$ 和 $\mathrm{B \: = \: B_{3}B_{2}B_{1}B_{0}}$。我们可以通过以下两种方式之一实现 4 位二进制加法器。

- 使用一个半加法器进行两个最低有效位的加法,使用三个全加法器进行三个较高有效位的加法。

- 使用四个全加法器以保持一致性。由于初始进位 Cin 为零,用于添加最低有效位的全加器变为半加器。

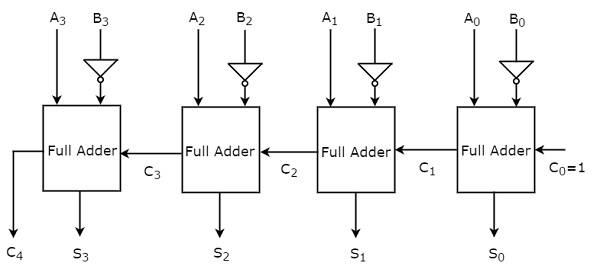

目前,我们考虑第二种方法。下图显示了 4 位二进制加法器的框图。

这里,4 个全加器级联。每个全加器都获取两个并行输入 A 和 B 的相应位。一个全加器的进位输出将是后续高阶全加器的进位输入。这个 4 位二进制加法器产生最多 5 位的结果和。因此,最后一级全加器的进位将是 MSB。

这样,我们只需级联所需数量的全加器即可实现任何高阶二进制加法器。这种二进制加法器也称为波纹进位(二进制)加法器,因为进位从一个阶段传播(波纹)到下一个阶段。

二进制减法器

执行两个二进制数减法的电路称为二进制减法器。我们可以通过以下两种方法实现二进制减法器。

- 级联全减法器

- 2 的补码方法

在第一种方法中,我们将通过级联"n"个全减法器来获得一个 n 位二进制减法器。因此,首先您可以实现半减法器和全减法器,类似于半加法器和全加法器。然后,您可以通过级联"n"个全减法器来实现一个 n 位二进制减法器。因此,我们将有两个独立的电路用于两个二进制数的二进制加法和减法。

在第二种方法中,我们可以使用相同的二进制加法器来减去两个二进制数,只需在第二个输入中进行一些修改即可。因此,内部会发生二进制加法运算,但输出是结果减法。

我们知道两个二进制数 A 和 A 的减法B 可以写成,

$$\mathrm{A-B \: = \: A \: + \: \left ( {2}'s \: compliment \: of \: B \right )}$$

$$\mathrm{\Rightarrow \: A \: - \: B \: = \: A \: + \: \left ( {1}'s \: compliment \: of \: B \right ) \: + \: 1}$$

4 位二进制减法器

4 位二进制减法器产生两个 4 位数的减法。设 4 位二进制数为 $\mathrm{A \: = \: A_{3}A_{2}A_{1}A_{0}}$ 和 $\mathrm{B \: = \: B_{3}B_{2}B_{1}B_{0}}$。4 位二进制减法器的内部操作与 4 位二进制加法器的操作类似。如果将二进制数 A 的正常位、二进制数 B 的补码位和初始进位(借位)Cin 作为一个整体应用于 4 位二进制加法器,则它变为 4 位二进制减法器。下图显示了 4 位二进制减法器的框图。

此 4 位二进制减法器产生最多 5 位的输出。如果二进制数 A 大于二进制数 B,则输出的 MSB 为零,其余位保持 A-B 的幅度。如果二进制数 A 小于二进制数 B,则输出的 MSB 为 1。因此,取输出的 2 的补码以获得 A-B 的幅度。

这样,我们只需级联所需数量的全加器并进行必要的修改,即可实现任何高阶二进制减法器。

二进制加法器/减法器

可用于随时执行两个二进制数的加法或减法的电路称为二进制加法器/减法器。二进制加法器和二进制减法器都包含一组级联的全加器。二进制数 A 的输入位直接应用于二进制加法器和二进制减法器。

二进制加法器和二进制减法器的全加器的输入有两个不同之处。

- 二进制加法器中,二进制数 B 的输入位直接应用于全加器;而二进制减法器中,二进制数 B 的补码位应用于全加器。

- 初始进位 C0 = 0 应用于 4 位二进制加法器;而初始进位(借位)C0 = 1 应用于 4 位二进制减法器。

我们知道,当另一个输入为零时,2 输入异或门 产生的输出与第一个输入的输出相同。类似地,当另一个输入为 1 时,它会产生一个输出,该输出是第一个输入的补码。

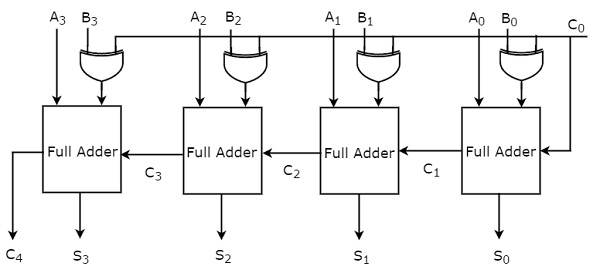

因此,我们可以将二进制数 B 的输入位应用于 2 输入异或门。所有这些异或门的另一个输入都是 C0。因此,根据 C0 的值,异或门会生成二进制数 B 的正常位或补码位。

4 位二进制加法器/减法器

4 位二进制加法器/减法器根据初始进位或借位的值 𝐶0 对两个 4 位数进行加法或减法。设 4 位二进制数 $\mathrm{A \: = \: A_{3}A_{2}A_{1}A_{0}}$ 和 $\mathrm{B \: = \: B_{3}B_{2}B_{1}B_{0}}$。4 位二进制加法器/减法器的操作与 4 位二进制加法器和 4 位二进制减法器的操作类似。

将二进制数 A 和 B 的正常位应用到 &初始进位或借位 C0 从外部传输到 4 位二进制加法器。下图显示了 4 位二进制加法器/减法器的框图。

如果初始进位 𝐶0 为零,则每个全加器都会获得二进制数 A 和 B 的正常位。因此,4 位二进制加法器/减法器产生的输出是两个二进制数 A 和 B 的加法。

如果初始借位 𝐶0 为一,则每个全加器都会获得二进制数 A 和 B 的正常位二进制数 B 的补码位。因此,4 位二进制加法器/减法器产生的输出是两个二进制数 A 和 B 的减法。

因此,借助附加异或门,同一电路可用于两个二进制数的加法和减法。