数字电子中的 CMOS 逻辑门

什么是逻辑门?

在数字电路中,逻辑门是数字电路或系统的基本元素,执行特定的逻辑运算。逻辑门通常有一个或多个输入和一个输出。逻辑门的输出与基于特定逻辑的输入相关。

一些常用的逻辑门是:与门、或门、非门、与非门和或非门。

什么是 CMOS 技术?

CMOS,即互补金属氧化物半导体,是用于制造集成电路 (IC) 的主要技术。该技术广泛用于制造各种数字电子元件,如微处理器、传感器、逻辑门等。

CMOS 技术采用 NMOS(N 沟道金属氧化物半导体)和 PMOS(P 沟道金属氧化物半导体)逻辑来实现不同类型的数字功能。

CMOS 技术因其关键优势而被广泛用于实现数字逻辑门,例如快速开关速度、低功耗、高电压范围、高噪声容限等。

基本 CMOS 逻辑门

现在让我们详细讨论基本的 CMOS 逻辑门。

CMOS 或门

或门是数字电子技术中的基本逻辑门。或门在其任意输入为高电平时产生高电平或逻辑 1 输出,在其所有输入为低电平时产生低电平或逻辑 0 输出。

下面给出了双输入或门的真值表。

| 输入 | 输出 | ||

|---|---|---|---|

| A | B | Y = A + B | |

| 0 | 0 | 0 | |

| 0 | 1 | 1 | |

| 1 | 0 | 1 | |

| 1 | 1 | 1 | |

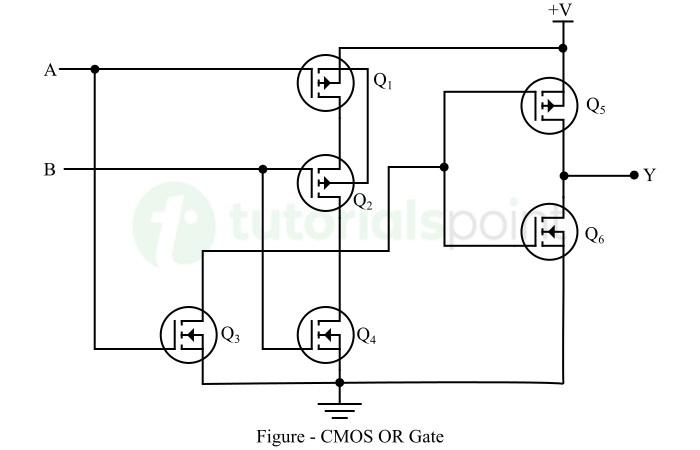

下图显示了 CMOS 逻辑中双输入或门的实现。

在这里,我们结合了多个CMOS 反相器组合在一起构成 CMOS 或门。在电路图中,CMOS 或门由 PMOS 晶体管和 NMOS 晶体管组成,它们并联在电源电压 (V) 和输出之间。

在上述电路中,当一个或两个输入(A 和 B)为高电平(逻辑 1)时,相应的 PMOS 和 NMOS 晶体管切换,使电流从输出流向地,导致输出端电压低(逻辑 0)。

当两个输入都为低电平(逻辑 0)时,相应的 CMOS 晶体管切换,使输出连接到电源电压,导致输出端电压高(逻辑 1)。

CMOS 与门

与门是各种数字逻辑电路中使用的基本逻辑门。 AND 门仅当其所有输入都为高电平时才会产生高电平或逻辑 1 输出,当其任何输入为低电平时,它会产生低电平或逻辑 0 输出。

双输入 AND 门的真值表如下所示。

| 输入 | 输出 | |

|---|---|---|

| A | B | Y = AB |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

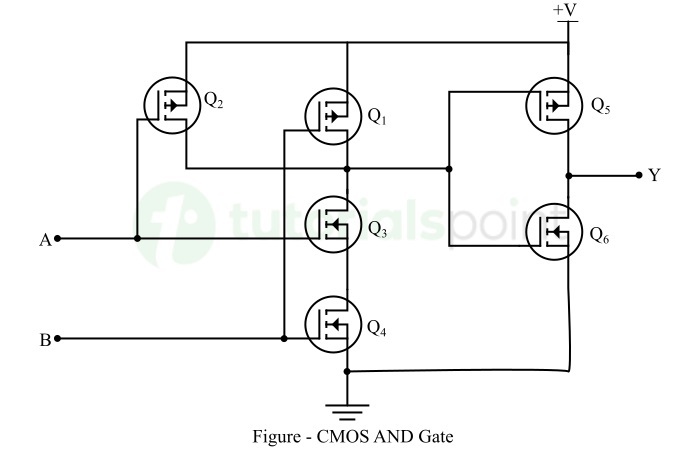

下图显示了使用 CMOS 技术实现的与门。

在这里,为了实现 CMOS 与门,我们将多个 CMOS 反相器连接在一起。在 CMOS 与门电路中,使用 PMOS 和 NMOS 晶体管来构建它。这些晶体管分别串联在电源电压 (V) 和输出 (Y) 之间,并联在输出和地之间。

对于上图所示的 CMOS 与门,当两个输入都为高电平(逻辑 1)时,CMOS 晶体管会切换,使输出连接到电源电压 (V),从而产生高电平(逻辑 1)输出。

当任何一个输入为低电平时,电路中的 CMOS 晶体管会切换,使电流从电源流向地,使输出为低电平(逻辑 0)。

CMOS 非门

非门也是数字逻辑电路中使用的基本逻辑门。非门只有一个输入和一个输出。当非门的输入为低电平或逻辑0时,其输出为高电平或逻辑1;当非门的输入为高电平或逻辑1时,其输出为低电平或逻辑0。

在CMOS逻辑门中,CMOS非门是最简单的CMOS逻辑门。它也被称为CMOS反相门。

非门的真值表如下。

| 输入 | 输出 |

|---|---|

| A | Y = A' |

| 0 | 1 |

| 1 | 0 |

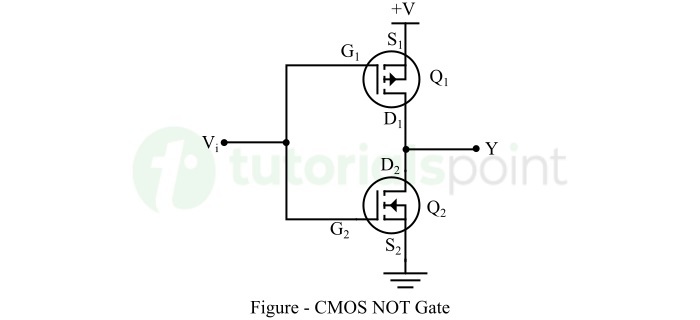

CMOS技术中非门的实现如下所示图。

此处,输入施加到两个 CMOS 晶体管的栅极端子,输出连接到它们的漏极端子。

当将正电压脉冲(逻辑 1)施加到输入 Vi 时,CMOS 晶体管 Q1 处于关闭状态,CMOS 晶体管 Q2 处于打开状态。因此,输出电压将处于接地电压,即逻辑 0。

当将接地电压(逻辑 0)施加到输入 Vi 时,CMOS 晶体管 Q1 处于打开状态,CMOS 晶体管 Q2 处于关闭状态。因此,输出将关闭到 +V,即逻辑 1。