数字电子器件中使用 2:1 MUX 的 AND 门

多路复用器 或 MUX 是一种组合电路,它接受多个数据输入,但只允许其中一个数据输入流过输出线。多路复用器 (MUX) 也称为数据选择器,因为它可以从多个数据中选择一个。

MUX 由 2n 条数据输入线、n 条选择线和 1 条输出线组成。因此,它将 2n 条输入线转换为 1 条输出线。因此,它也被称为多对一设备。

根据输入线的数量,存在几种类型的多路复用器,例如 2:1 MUX、4:1 MUX、8:1 MUX 等。

因为,本文旨在解释如何使用 2:1 MUX 实现 AND 门。因此,让我们详细讨论一下 2:1 MUX。

什么是 2:1 多路复用器 (MUX)?

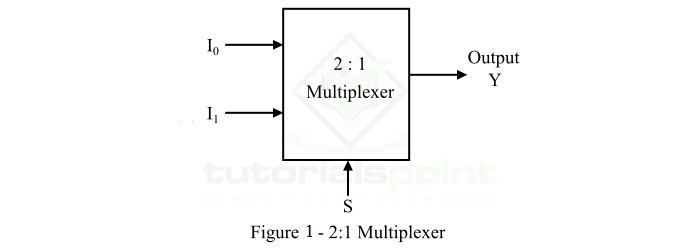

2:1 MUX 的功能框图如图 1 所示。

2:1 MUX 由 2 (21) 条数据输入线(由 I0 和 I1 指定)、1 条选择线(由 S 指定)和 1 条输出线 Y 组成。施加到选择线 S 的逻辑电平 0 或 1 决定了哪些输入数据将通过多路复用器的输出线。

2:1 多路复用器的真值表

多路复用器的操作2:1 MUX 可以借助下面显示的真值表进行分析。

| 选择线 (S) | 输出 (Y) |

|---|---|

| 0 | I0 |

| 1 | I1 |

从这个真值表中,我们可以得出结论,

- 如果选择线 S 连接到逻辑电平 0,则连接到 I0 的数据输入将通过输出线Y。

- 如果选择线 S 连接到逻辑电平 1,则连接到 I1 的数据输入将通过输出线 Y。

现在,让我们讨论与门的基础知识。

什么是与门?

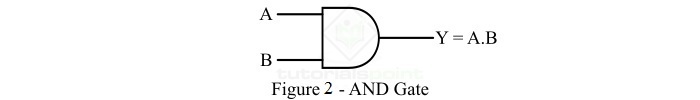

与门 是一种基本逻辑门,可能有两个或多个输入,但只有一个输出。如果与门的任何一个输入处于逻辑 0 状态,则与门给出逻辑 0 状态(低)作为输出,否则,它给出逻辑 1 状态(高)作为输出。因此,只有当与门的所有输入都为高或逻辑 1 状态时,其输出才为高或逻辑 1 状态。图 2 显示了双输入与门的逻辑符号。

双输入与门的逻辑表达式为:

$$\mathrm{Y\:=\:A\:\cdot \: B}$$

其中,"." (点) 符号表示与运算。读作"Y 等于 A 与 B"。

借助下面给出的函数表,可以理解与门的运算。

| 输入 | 输出 | |

|---|---|---|

| A | B | Y = A·B |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

在了解了与门和 2:1 MUX 的基础知识后,我们能够借助下一节中描述的 2:1 MUX 实现与门。

使用 2:1 多路复用器实现与门

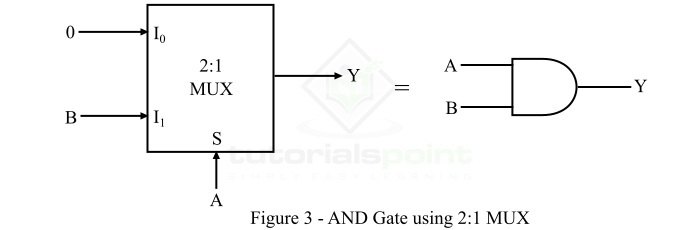

图 3 显示了与门等效的 2:1 多路复用器的功能框图。

此处,2:1 MUX 的输入线 I0 设置为逻辑 0 状态。与门的输入 B 应用于 MUX 的输入线 I1。 AND 门的输入变量 A 用于控制 MUX 的选择线。

2:1 MUX 作为 AND 门的操作可以描述如下 −

- 当 A = 0 时,MUX 作为 AND 门的输出为 0。

- 当 A = 1 时,MUX 作为 AND 门的输出等于 B。

2:1 MUX 作为 AND 门工作的功能表如下,

| A (S) | B | Y | 说明 |

|---|---|---|---|

| 0 | 0 | 0 | Y = 0 当 A = 0 时 |

| 1 | 0 | 0 | |

| 1 | 0 | 0 | Y = B 当 A = 1 时 |

| 1 | 1 | 1 |

因此,我们可以分析如下,

$$\mathrm{Y\:=\:\bar{A}\:\cdot \: \bar{B} \: \cdot \: 0 \: + \: \bar{A} \: \cdot \: B \cdot 0 \: + \: A \: \cdot \bar{B} \cdot 0 \: + \: A \: \cdot \bar{B} \cdot 0 \: = \: AB}$$

这样,我们可以使用2:1 多路复用器。