JK 触发器中的竞争条件

在开始讨论竞争条件之前,我们先来简单介绍一下 JK 触发器及其框图和真值表。

JK 触发器

JK 触发器 是一种具有两个稳定状态的 1 位存储设备。 JK 触发器的框图如图 1 所示。

它有两个输入,分别表示为"J"和"K",一个时钟输入用于同步电路,两个输出分别表示为 Q 和 Q'。

当没有时钟信号时,JK 触发器的输出与输入 J 和 K 无关。当有时钟信号时,JK 触发器的输出根据输入 J 和 K 而变化。

JK 触发器的真值表

JK 触发器的操作可以从其真值表中研究,如下所示 −

| 输入 | 上一个状态 | 输出(下一个状态) | 注释 | |

|---|---|---|---|---|

| J | K | Qn | Qn+1 | |

| 0 | 0 | 0 | 0 | 无变化 |

| 0 | 0 | 1 | 1 | 无变化 |

| 0 | 1 | 0 | 0 | 重置 |

| 0 | 1 | 1 | 0 | 重置 |

| 1 | 0 | 0 | 1 | 设置 |

| 1 | 0 | 1 | 1 | 设置 |

| 1 | 1 | 0 | 1 | 切换 |

| 1 | 1 | 1 | 0 | 切换 |

现在,让我们讨论一下 JK 触发器中的竞争条件。

JK 触发器中的竞争条件

从上面的 JK 触发器真值表可以看出,当 J = 1 且 K =1 时,输出 Qn+1 = Qn',这意味着对于输入 J = 1 和 K = 1,JK 触发器充当拨动开关。

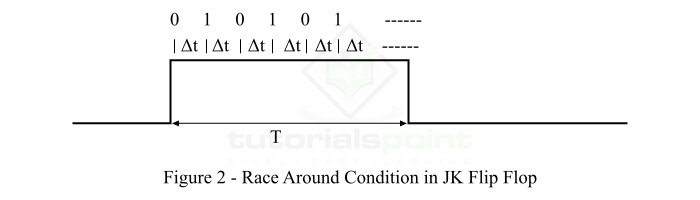

让我们考虑输入 J = 1 和 K = 1,输出 Q = 0。在触发器的传播延迟(设 Δt)之后,JK 触发器的输出从 0 变为 1。众所周知,JK 触发器的输出与其输入相连。因此,输出也充当输入,因此在下一个延迟(Δt)之后,输出将从 1 变为 0。此过程将持续到施加的时钟信号结束。因此,JK 触发器的输出是不确定的。JK 触发器的这种情况称为竞态条件。

JK 触发器中的竞态条件如图 2 所示,其中 T 是时钟脉冲的总持续时间。

如何避免竞态条件?

在时钟脉冲存在期间输入不变的触发器中不存在竞态条件问题。但是,在 JK 触发器的情况下,由于输入和输出之间存在反馈路径,输入在时钟脉冲期间会发生变化。因此,在 JK 触发器中,竞争条件是一个主要问题。

可以通过增加触发器的延迟来避免竞争条件问题和输出的不确定性。为此,触发器的延迟必须大于时钟信号的持续时间,即 Δt > T。换句话说,必须减少施加的时钟信号的持续时间 (T),使其小于触发器的延迟 (Δt)。

但是,增加触发器的延迟并不是一个好的做法,因为它会降低系统的速度。另一方面,将时钟脉冲的持续时间 (T) 减少到超过触发器的延迟 (Δt) 也相当困难。这是因为,JK 触发器的延迟(Δt)是纳秒级的。

因此,解决 JK 触发器中的竞争条件问题的最实用方法是使用主从模式中的 JK 触发器。在 JK 触发器的主从模式下,两个 JK 触发器级联。

这就是 JK 触发器中的竞争条件及其补救措施。