异步或非时钟 SR 触发器

什么是 SR 触发器?

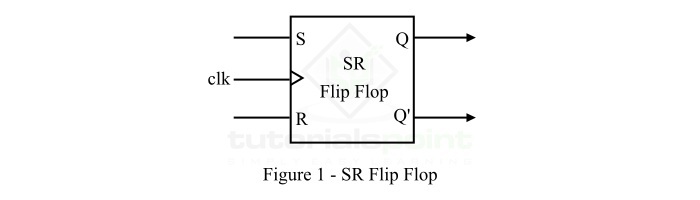

在数字电子技术中,SR 触发器是一种顺序逻辑电路,具有两个输入,即 S 和 R,以及两个输出,即 Q 和 Q'。

输入 S 表示"设置",输入 R 表示"重置"。输出 Q 是触发器的正常输出,Q' 是触发器的反相输出,它是触发器正常输出 Q 的补码。 SR 触发器是一种单比特存储设备,用于多种数字电子系统。

SR 触发器的基本框图如图 1 所示。

根据时钟信号的存在与否,SR 触发器可分为两种类型,即 同步 SR 触发器 和 异步 SR 触发器。同步 SR 触发器仅在时钟信号激活时才产生输出。因此,它也被称为时钟 SR 触发器。

另一方面,异步 SR 触发器是只要将输入应用于电路,其输出就可用的触发器。异步 SR 触发器也称为非时钟 SR 触发器,因为其输出不受时钟信号控制,而仅受施加的输入控制。

正如本文标题所暗示的,这里我们只讨论异步或非时钟 SR 触发器。

什么是异步 SR 触发器?

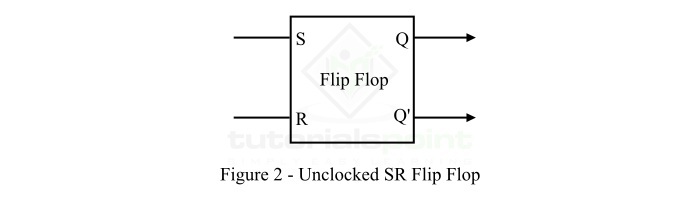

异步 SR 触发器,也称为非时钟 SR 触发器或简称为 SR 锁存器,是一种顺序逻辑电路,用于存储一位二进制信息。它有两个输入和两个输出。输入是触发器的 S(表示"设置"输入)和 R(表示"重置"输入)。第一个输出是 Q,称为触发器的正常输出,另一个输出是 Q',称为互补输出。

异步或非时钟 SR 触发器的框图如图 2 所示。

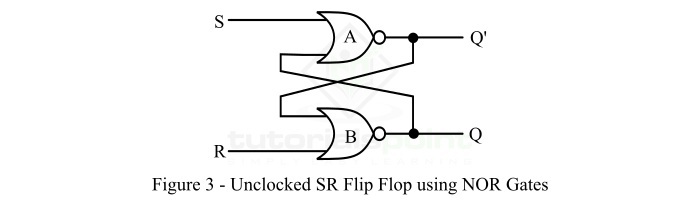

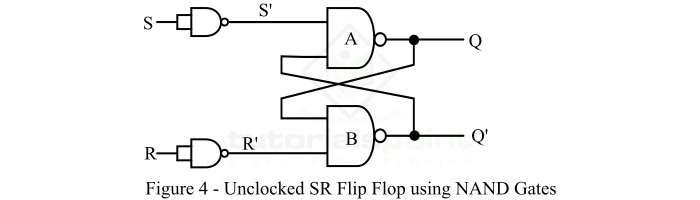

非时钟或异步 SR 触发器可以通过使用两个交叉耦合的 NOR 门或 NAND 门来构造。

现在让我们讨论 SR 触发器的每种构造(使用 NOR 门和使用 NAND 门)及其操作和真值表。

使用 NOR 门的异步 SR 触发器

如前所述,非时钟 SR 触发器可以通过使用两个交叉耦合的NOR 门如图 3 所示。

它有两个输入,即 S(设置) 和 R(重置),以及两个输出,即 Q(正常输出) 和 Q'(反相输出)。

对于输入 S 和 R 的不同可能组合,此异步 SR 触发器按如下所述运行 −

- 当 S = 0 且 R = 0 − 在这种情况下,两个 NOR 门的输入均为逻辑 0。因此,对电路的输出没有影响。因此,输出仍保持其先前的状态。无时钟 SR 触发器的这种条件称为"无变化"或"保持条件"。

- 当 S = 1 且 R = 0 − 在这种情况下,NOR 门 A 的输出将变为零,因为输入 S 为逻辑 1。因此,NOR 门 B 的两个输入都变为逻辑 0,因此,NOR 门 B 的输出为逻辑 1,使 Q 等于 1。这称为无时钟 SR 触发器的"设置条件"。

- 当 S = 0 且 R = 1 −在这种情况下,NOR 门 B 的输出将变为零,因为输入 R 为逻辑 1,即 Q = 0。结果,NOR 门 A 的两个输入都变为逻辑 0,因此,NOR 门 A 的输出为逻辑 1,使 Q' 等于 1 且 Q = 0。这称为无时钟 SR 触发器的"复位条件"。

- 当 S = 1 且 R = 1 − 这称为 SR 触发器的"禁止条件或无效状态",因为这种输入组合迫使两个 NOR 门的输出变为逻辑 0,这是不可能的。

SR 触发器的真值表

基于上述操作的无时钟 SR 触发器的真值表如下所示。

| S | R | Q | 描述 |

|---|---|---|---|

| 0 | 0 | NC | 无变化 |

| 0 | 1 | 0 | 重置 |

| 1 | 0 | 1 | 设置 |

| 1 | 1 | X | Forbidden |

使用 NAND 门的异步 SR 触发器

我们还可以使用两个交叉耦合的 NAND 门来实现无时钟 SR 触发器。使用 NAND 门的异步 SR 触发器如下图 4 所示。

可以看出,异步 SR 触发器是一个低电平有效输入 SR 触发器。现在,让我们讨论异步 SR 触发器在不同可能输入组合下的工作情况。

- 当 S = 0 且 R = 0 时,即 S' = 1 且 R' = 1 − 在这种情况下,两个输入(即 S' 和 R')均为逻辑 1,因此输出保持先前状态。这称为 SR 触发器的保持状态。

- 当 S = 0 且 R = 1 时,即 S' = 1 且 R' = 0 −在这种情况下,输入 S' 为逻辑 1,输入 R' 为逻辑 0。因此,NAND 门 B 的输出将变为逻辑 1。因此,NAND 门 A 的输出,即 Q 变为逻辑 1。这称为触发器的复位状态。

- 当 S = 1 且 R = 0 时,即 S' = 0 且 R' = 1 − 在这种情况下,输入 S' 为逻辑 0,输入 R' 为逻辑 1。由于输入 S' 为逻辑 0,因此 NAND 门 A 的输出,即 Q 变为逻辑 1。这称为 SR 触发器的置位状态。

- 当 S = 1 且 R = 1 时,即 S' = 0 且 R' = 0 −在这种情况下,两个输入都是逻辑 0,即两个 NAND 门的输出必须为逻辑 1,这是不允许的,因为输出必须互相补充。这被称为触发器的禁止或无效状态。

使用 NAND 门的异步 SR 触发器的真值表

基于此讨论,我们可以推导出使用 NAND 门实现的异步 SR 触发器的真值表。

| S | S' | R | R' | Q | 描述 |

|---|---|---|---|---|---|

| 0 | 1 | 0 | 1 | NC | 无变化 |

| 0 | 1 | 1 | 0 | 0 | 重置 |

| 1 | 0 | 0 | 1 | 1 | 设置 |

| 1 | 0 | 1 | 0 | X | 禁止 |

这都是关于数字电子产品中的异步或非时钟 SR 触发器。