多路复用器通用逻辑门

阅读本章,了解如何使用多路复用器实现通用逻辑门。我们先来简单介绍一下多路复用器和通用逻辑门。

什么是多路复用器?

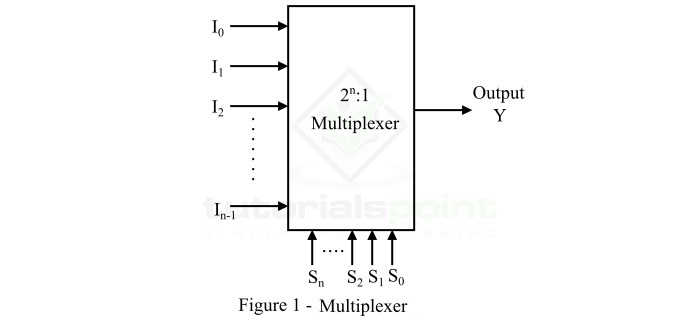

多路复用器或MUX或数据选择器是一种组合逻辑电路,它接受多个数据输入,但每次只允许其中一个通过输出通道。多路复用器的框图如图 1 所示。

多路复用器由 2n 条数据输入线、n 条选择线和一条输出线组成。应用于选择线的逻辑电平决定哪个输入将传递到输出通道。

根据数据输入线的数量,多路复用器可以有几种类型,例如 2:1 MUX、4:1 MUX、8:1 MUX 等。在数字电子技术中,多路复用器用于多种应用,例如实现布尔函数和不同类型的逻辑门。

什么是通用门?

通用逻辑门是一种逻辑门(用于执行逻辑运算的数字设备),可用于实现任何类型的逻辑函数或其他基本逻辑门,例如 OR、AND、NOT 等。

在数字电子技术中,我们有两个通用逻辑门,即 NAND 门 和 NOR 门。

NAND 门

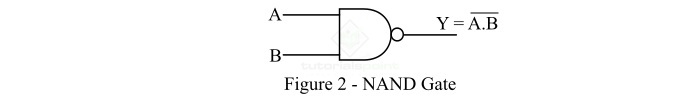

NAND 门是一种通用逻辑门。 NAND 门基本上是两种基本逻辑门的组合,即 AND 门和非门,即

NAND 逻辑 = AND 逻辑 + NOT 逻辑

NAND 门是一种逻辑门,当其所有输入都为高时,其输出为低,当其任何输入为低时,其输出为高。因此,NAND 门的操作与 AND 门的操作相反。图 2 显示了双输入 NAND 门的逻辑符号。

对于 NAND 门,如果 A 和 B 是输入变量,Y 是输出变量,则其输出方程为:

$$\mathrm{Y \: = \: \overline{A \: \cdot \: B} \: = \: \left ( A \: \cdot \: B \right )'}$$

读作"Y 等于 A.B 整条"。

可以借助下面给出的真值表来分析 NAND 门对不同可能输入组合的操作−

| 输入 | 输出 | |

|---|---|---|

| A | B | Y = (A.B)' |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

或非门

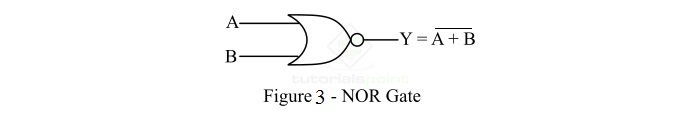

或非门是另一种通用逻辑门。这里,NOR 表示 NOT + OR。这意味着,OR 输出被 NOT 或反转。因此,NOR 门是 OR 门和非门的组合,即

NOR 门 = OR 门 + NOT 门

NOR 门是一种逻辑门,只有当其所有输入都为 LOW 时,其输出才为 HIGH,即使其任何输入变为 HIGH,其输出也为 LOW。图 3 显示了双输入 NOR 门的逻辑符号。

对于 NOR 门,如果 A 和 B 是输入变量,Y 是输出变量,则 NOR 门的输出方程为:

$$\mathrm{Y \: = \: \overline{A \: + \: B} \: = \: \left ( A \: + \: B \right )'}$$

读作"Y 等于 A 加 B 整条"。

我们可以通过下面给出的真值表分析 NOR 门在不同可能输入组合下的操作 −

| 输入 | 输出 | |

|---|---|---|

| A | B | Y = (A+B)' |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

现在,在简要介绍了多路复用器、NAND 门和 NOR 门之后,我们可以讨论如何使用多路复用器实现这些通用逻辑门。

使用多路复用器的 NAND 门

图 4 显示了使用多路复用器的双输入 NAND 门的实现。

由于双输入 NAND 门可以有总共四种(22 = 4)可能的输入变量组合。因此,要实现双输入 NAND 门,我们需要一个 4:1 MUX。

根据双输入 NAND 门的真值表,前三个组合(即 00、01、10)的输出 Y = 1。因此,多路复用器的输入线 I0、I1 和 I2 连接到逻辑 1。组合 11 时,NAND 门的输出 Y = 0,因此,MUX 的输入线 I3 连接到逻辑 0。

这样,我们就可以使用多路复用器实现 NAND 门。现在,让我们讨论使用多路复用器实现 NOR 门。

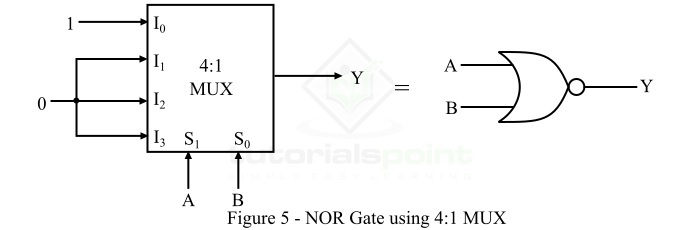

使用多路复用器的 NOR 门

使用多路复用器实现双输入 NOR 门如图 5 所示。

由于双输入 NOR 门总共可以有四种 (22 = 4) 种可能的输入变量组合。因此,要实现双输入 NOR 门,我们需要一个 4:1 MUX。

NOR 门的输入变量 A 和 B 用作多路复用器的选择线。其中,A 和 B 分别应用于 S1 和 S0。

根据双输入 NOR 门的真值表,仅对于输入变量的第一个组合,即 00,输出 Y = 1。因此,我们仅将逻辑 1 应用于多路复用器的数据输入线 I0。对于所有其他组合(即 01、10 和 11),NOR 门的输出 Y = 0,因此,MUX 的输入线 I1、I2 和 I3 连接到逻辑 0。这样,可以使用多路复用器实现 NOR 门。

解决问题

尝试解决以下教程问题,以在使用多路复用器实现通用逻辑门的概念方面表现出色。

Q. 1 − 使用 8:1 MUX 实现三输入 NAND 门。

Q. 2 − 使用 8:1 MUX 实现三变量 NOR 门。