算法状态机

每个数字系统都可以分为两部分。即数据路径(数字)电路和控制电路。数据路径电路执行诸如存储二进制信息(数据)和将数据从一个系统传输到另一个系统等功能。而控制电路则决定数字电路的操作流程。

使用状态图很难描述大型状态机的行为。为了克服这一困难,可以使用算法状态机 (ASM) 图。ASM 图类似于流程图。它们用于表示数据路径电路和控制电路要执行的任务流程。

ASM 图的基本组件

以下是 ASM 图的三个基本组件。

- 状态框

- 决策框

- 条件输出框

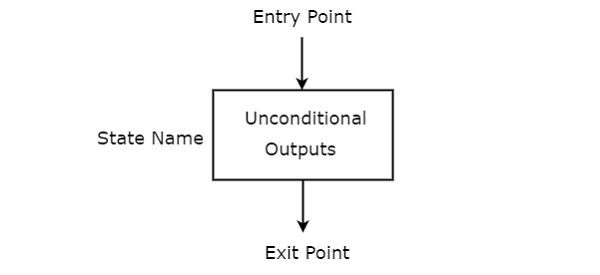

状态框

状态框以矩形表示。每个状态框代表顺序电路的一个状态。状态框的符号如下图所示。

它有一个入口点和一个出口点。状态名称放在状态框的左侧。与该状态相对应的无条件输出可以放在状态框内。 Moore 状态机输出也可以放在状态框内。

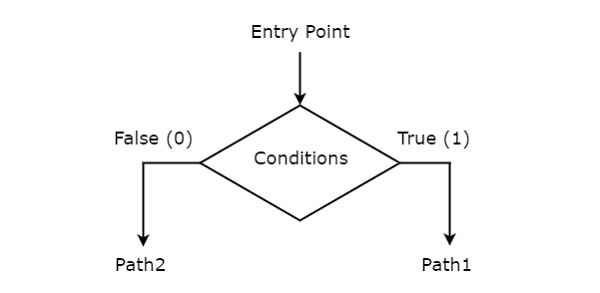

决策框

决策框以菱形表示。决策框的符号如下图所示。

它有一个入口点和两个出口路径。输入或布尔表达式可以放在决策框内,需要检查它们是真还是假。如果条件为真,那么它将优先选择路径 1。否则,它将优先选择路径 2。

条件输出框

条件输出框以椭圆形表示。条件输出框的符号如下图所示。

与状态框类似,它也有一个入口点和一个出口点。条件输出可以放在状态框内。一般来说,Mealy状态机输出表示在条件输出框内。因此,根据需求,我们可以适当使用上述组件来绘制ASM图表。