数字电子技术 - 时序电路

数字电路分为两大类,即组合电路和时序电路。我们已经在本教程的前面几章中讨论了组合电路。本章将重点介绍时序电路的细节。

时序电路是一种数字逻辑电路,其输出取决于电路的当前输入以及过去的操作。让我们从时序电路的基本介绍开始本教程的这一部分。

什么是时序电路?

时序电路是一种逻辑电路,它由一个存储元件组成,用于存储电路过去操作的历史记录。因此,时序电路的输出取决于电路的当前输入以及过去的输出。

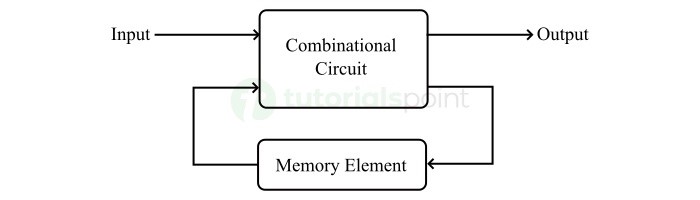

下图显示了典型时序电路的框图 −

从这里可以看出,时序电路基本上是组合电路和存储元件的组合。组合电路执行指定的逻辑操作,而存储元件记录电路的操作历史。然后,此历史记录将用于将来执行各种逻辑操作。

时序电路之所以如此命名,是因为它们使用一系列最新和先前的输入来确定新的输出。

时序电路的主要组件

时序电路由几个不同的数字组件组成,用于处理和保存系统中的信息。这里解释了时序电路的一些关键组件 −

逻辑门

AND、OR、NOT 等逻辑门用于实现时序电路的数据处理机制。这些逻辑门基本上以特定方式互连,以实现组合电路来对输入数据执行逻辑运算。

存储元件

在时序电路中,存储元件是另一个保存电路操作历史的关键组件。一般情况下,触发器用作时序电路中的存储元件。

在时序电路中,输出和输入之间提供反馈路径,将信息从输出端传输到存储元件,再从存储元件传输到输入端。

所有这些组件互连在一起,设计出一个时序电路,可以执行复杂的操作并将状态信息存储在存储元件中。

时序电路的类型

根据结构、操作和应用,时序电路分为以下两种类型 −

- 异步时序电路

- 同步时序电路

让我们详细讨论这两种时序电路。

异步时序电路

一种操作不依赖于时钟信号的时序电路是称为异步时序电路。这种类型的时序电路使用输入脉冲进行操作,这意味着它们的状态随着输入脉冲的变化而变化。

异步时序电路的主要组件包括非时钟触发器和组合逻辑电路。下图显示了典型异步时序电路的框图。

从该图中可以看出,异步时序电路类似于具有反馈机制的组合逻辑电路。

异步时序电路主要用于时钟信号不可用或不实用的应用中。例如,在任务执行速度很重要的情况下。

异步时序电路设计起来相对困难,有时它们会产生不确定的输出。

波纹计数器是异步时序电路的常见示例。

同步时序电路

同步时序电路是一种时序电路,其中所有存储器元件都由公共时钟信号同步。因此,同步时序电路将时钟信号与输入信号一起接收。

在同步时序电路中,输出脉冲的持续时间等于所施加时钟脉冲的持续时间。查看典型同步时序电路的框图 −

在此图中,可以看到时序电路的存储元件由时钟信号同步。

同步时序电路的主要缺点是其操作相当慢。这是因为每次电路都必须等待时钟脉冲才能进行操作。然而,同步时序电路最显著的优势在于它们具有可靠且可预测的操作。

同步时序电路的一些常见示例包括计数器、寄存器、存储器单元、控制单元等。

时序电路与组合电路

下面列出了使用时序电路相对于组合逻辑电路的一些主要优势 −

- 时序电路可以保留操作历史记录,这在各种应用中都很重要,例如数据存储、反馈控制系统等。

- 时序电路表现出动态行为,可以实时执行复杂操作。

- 时序电路包含反馈机制,可提高稳定性并优化系统性能。

- 同步时序电路使用公共时钟信号进行同步,以确保电路可靠运行。

- 时序电路可以使用电路设计比组合电路更简单。因此,它们的硬件复杂性较低。

序贯电路的缺点

序贯电路也有几个缺点。使用顺序电路的一些主要缺点如下 −

- 顺序电路具有较高的传播延迟,因为输入信号经过多级逻辑电路和存储元件。

- 顺序电路相对复杂,设计和分析过程耗时。

- 顺序电路需要适当的同步和时钟分配才能按预期工作。

- 与组合电路相比,顺序电路由于复杂的设计和使用时钟和存储元件等附加组件而消耗相对更多的功率。

顺序电路的应用

顺序电路在数字电子领域有着广泛的应用。以下是顺序电路应用的一些常见示例 −

- 顺序电路用于数字计数器,用于分频、事件计数、计时等应用更多。

- 时序电路还用于数字存储设备,如触发器、寄存器等,以存储和检索数据。

- 时序电路用于设计数字系统中的控制电路。

- 时序电路在时序逻辑和基于状态的数据处理操作中起着重要作用。

- 时序电路还用于自动化系统,以根据预定义的逻辑控制机器的运行。

- 在通信系统中,时序电路用于实现通信协议和数据传输标准。

结论

时序电路是数字电子系统中的重要组成部分。时序电路不过是组合逻辑电路和存储元件的组合,其中存储元件通过反馈机制与组合电路相连。

关于时序电路,最重要的是要注意,它们的输出由当前输入和先前的输入和输出决定。

时序电路用于设计复杂的数字系统,可以执行高级操作,如实时数据处理、数据存储和传输、计数事件等。