SR 触发器转换为 JK 触发器

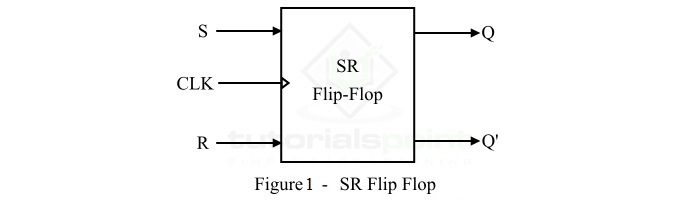

什么是 SR 触发器?

SR 触发器 是一个简单的 1 位存储元件,具有两个输入,即 S 和 R,以及两个输出,即 Q 和 Q'。其中,S 指定设置输入,R 指定重置输入。输出 Q 是正常输出,Q' 是互补或反相输出。除了 SR 输入外,SR 触发器还具有用于触发电路的时钟输入。

SR 触发器的框图如下图 1 所示。

可以使用下面给出的真值表来分析 SR 触发器的操作。

| 输入 | 输出 | |

|---|---|---|

| S | R | Qn+1 |

| 0 | 0 | Qn |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | Forbidden |

这里,Qn+1是下一个状态,Qn是输出的当前状态。

SR触发器的特征方程为:

$$\mathrm{Q_{n+1} \: = \: S+R'Q_{n}}$$

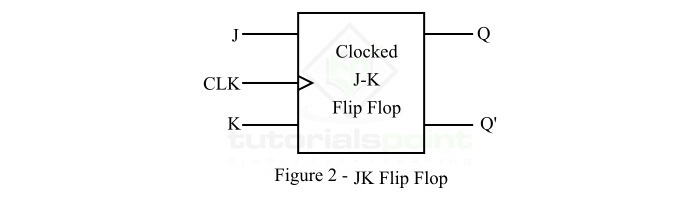

什么是JK触发器?

JK触发器也是一个1位存储设备,有两个输入,类似于SR触发器,但它的输入用J和K表示,而不是S和R。它有两个输出,即Q(正常输出)和Q'(反相输出)。时钟信号用于电路同步。

JK 触发器的框图如下图 2 所示。

JK 触发器的操作可以通过下面给出的真值表来理解 -

| 输入 | 输出 | |

|---|---|---|

| J | K | Qn+1 |

| 0 | 0 | Qn |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | Toggle |

JK触发器的特征方程为:

$$\mathrm{Q_{n+1}=JQ_{n}'+K'Q_{n}}$$

在讨论了SR触发器和JK触发器的基础知识之后。现在让我们讨论SR触发器到JK触发器的转换。

触发器的转换

我们可以将一种类型的触发器转换为另一种类型的触发器。触发器的转换过程涉及以下步骤-

步骤1 − 写出触发器的激励表。

步骤2 −借助卡诺图(K-map)简化激励表。

步骤3 − 绘制所需的逻辑电路图。

现在,让我们将SR触发器转换为JK触发器。

SR触发器转换为JK触发器

按照触发器转换的步骤,下面描述了SR触发器转换为JK触发器的过程。

步骤1 − SR 触发器转换为 JK 触发器的激励表如下所示 -

| 输入 | 输出的当前状态 | 输出的下一个状态 | 触发器输入 | ||||

|---|---|---|---|---|---|---|---|

| J | K | Qn | Qn+1 | S | R | S | R |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | X |

| 0 | 1 | ||||||

| 0 | 0 | 1 | 1 | 0 | 0 | X | 0 |

| 1 | 0 | ||||||

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | X |

| 0 | 1 | ||||||

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | X | 0 |

| 1 | 0 | ||||||

| 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

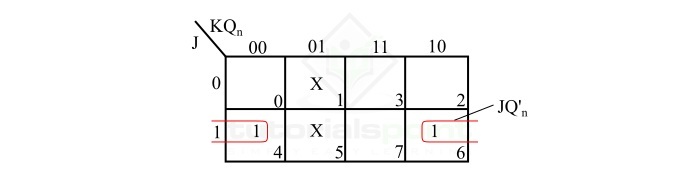

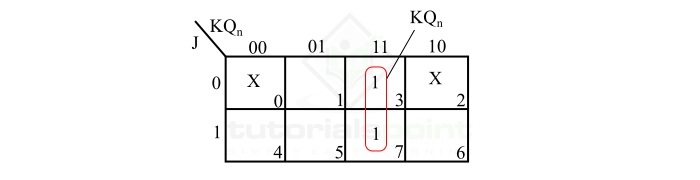

步骤 2 − 使用 K-Map − 简化输入表达式的激励

S 的 K-Map 简化为,

S = JQn'

R 的 K-map 简化为,

R = KQn

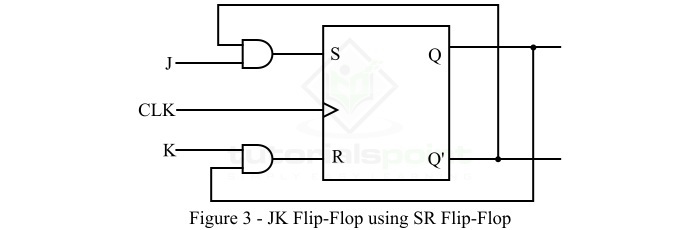

步骤 3 −最后,利用SR触发器画出JK触发器的逻辑图,如下图3所示。

这样,我们就可以将SR触发器转换为JK触发器了。