数字电子技术中的或门

在数字电子技术中,或门是一种具有两条或更多条输入线和一条输出线的基本逻辑门。它执行布尔加法功能。

在本章中,我们将解释或门的理论。在这里,我们将介绍或门的定义、其逻辑符号、布尔表达式、真值表、运算和电路。

那么,让我们从或门的基本定义开始。

什么是或门?

或门是一种用于执行逻辑加法的逻辑门。它可以有两个或多个输入和一个输出。

仅当所有输入都为低或逻辑 0 时,或门的输出才为低或逻辑 0。对于其他输入组合,或门的输出为高或逻辑 1。

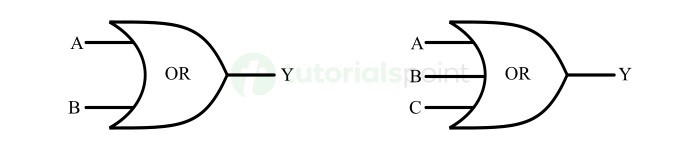

下图显示了双输入和三输入或门的逻辑符号。

这里,A、B 和 C 是输入线,Y 是输出线。

或门的真值表

真值表是显示不同输入组合与输出之间关系的表格。

以下是双输入或门的真值表 −

| 输入 | 输出 | |

|---|---|---|

| A | B | Y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

下表显示了三输入或门的真值表 −

| 输入 | 输出 | ||

|---|---|---|---|

| A | B | C | Y |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

从这两个真值表中,我们可以观察到,只有当或门的所有输入均为逻辑 0 或低时,或门的输出才为逻辑 0 或低。否则,或门的输出为高或逻辑 1。

或门的布尔表达式

布尔表达式是一个逻辑函数,它描述了或门的输入和输出之间的数学关系。

双输入或门的布尔表达式如下所示 −

Y = A + B

这里,A 和 B 是输入变量,Y 是输出变量。这个表达式读作"Y 等于 A 或 B"。这里,"+"号表示或运算。

类似地,三输入或门的布尔表达式如下所示 −

Y = A + B + C

这里,A、B和C是输入,Y是输出。

同样,我们可以将此表达式扩展到任意数量的输入变量。

或门的工作原理

对于不同输入组合,两输入或门的运算如下所示 −

- 如果 A = 0 且 B = 0,则或门的输出为 Y = 0。

- 如果 A = 0 且 B = 1,则或门的输出为 Y = 1。

- 如果A = 1 且 B = 0,或门的输出为 Y = 1。

- 如果 A = 1 且 B = 1,或门的输出为 Y = 1。

该理论解释,当施加到或门的两个输入都为低或逻辑 0 时,或门的输出也为低或逻辑 0,否则为高或逻辑 1。

类似地,三输入或门的工作原理如下 −

- 如果 A = 0、B = 0 和 C = 0,或门的输出为 Y = 0。

- 如果 A = 0、B = 0 和 C = 1,或门的输出为 Y = 1。

- 如果 A = 0、B = 1 和 C = 0,或门的输出为 Y = 1.

- 如果 A = 0、B = 1 且 C = 1,则或门的输出为 Y = 1。

- 如果 A = 1、B = 0 且 C = 0,则或门的输出为 Y = 1。

- 如果 A = 1、B = 0 且 C = 1,则或门的输出为 Y = 1。

- 如果 A = 1、B = 1 且 C = 0,则或门的输出为 Y = 1。

- 如果 A = 1、B = 1 且 C = 1,则或门的输出为 Y = 1。

该理论还解释了,只有当所有三个输入都为低或逻辑 0 时,或门的输出才为低或逻辑 0。

使用晶体管

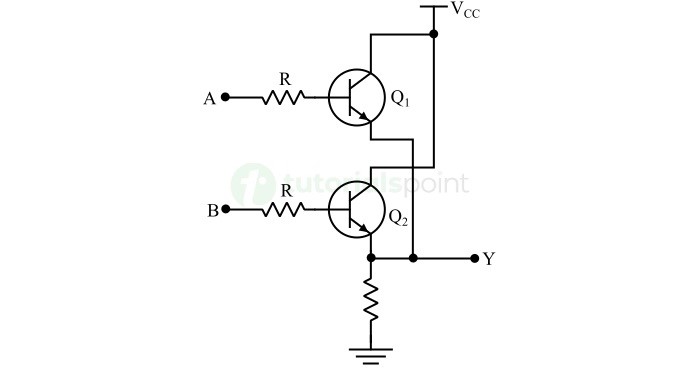

我们可以使用晶体管实现或门逻辑电路。下图显示了使用 BJT 晶体管实现的双输入或门。

此或门电路也称为晶体管-晶体管逻辑 (TTL) 或门。

晶体管或门的工作原理

下面解释了上面显示的晶体管或门电路的操作 −

当输入 A 和 B 都为低电平时,即 A 和 B 都连接到低电压 (0 V),晶体管 Q1 和 Q2 保持关闭状态并充当打开的开关。结果是输出线将直接连接到地电位。这使得电路的输出为低电平或逻辑 0。

如果输入 A 为低电平且输入 B 为高电平,晶体管 Q1 将关闭,晶体管 Q2 将打开并充当闭合的开关。因此,电源电压 VCC 将通过晶体管 Q2 连接到输出线。因此,电路的输出为高电平或逻辑 1。

如果输入 A 为高电平而输入 B 为低电平,晶体管 Q1 将导通,而晶体管 Q2 将充当断开的开关。因此,输出线将通过晶体管 Q1 连接到电源 VCC。因此,电路的输出为高电平或逻辑 1。

当输入 A 和 B 都为高电平时,晶体管 Q1 和 Q2 都将导通并充当闭合的开关。输出线将通过两个晶体管连接到电源 VCC,这使得电路的输出为高电平或逻辑 1。

该理论解释道,当电路的两个输入都连接到逻辑 0 或低电平信号时,输出为低电平或逻辑 0,否则输出为高电平或逻辑 1。因此,该电路实现了或门功能。

我们可以在电路中添加更多晶体管来实现更高阶的或门。

使用开关的或门

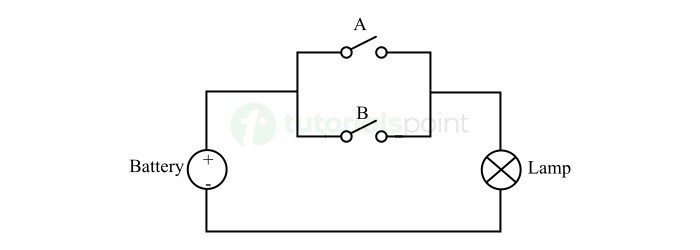

我们还可以使用电开关、电池和灯来实现或逻辑运算。下图描绘了双输入或门的开关电路图。

下面解释了此电路的工作原理 −

当开关 A 和 B 都打开时,电流流动的路径是闭合的。因此,灯将保持关闭状态,代表低或逻辑 0 输出。

如果开关 A 断开而开关 B 闭合,则电流通过开关 B 的路径是闭合的。在这种情况下,灯将发光并代表高或逻辑 1 输出。

如果开关 A 闭合而开关 B 断开,则电流通过开关 A 的路径是闭合的。在这种情况下,灯将发光并代表高或逻辑 1 输出。

如果开关 A 和 B 都闭合,则电流流动的路径是闭合的。这也会打开灯并代表高或逻辑 1 输出。

这样,上面显示的开关电路实现了或门操作。我们可以并行添加更多开关来实现更高阶的或门逻辑。

或门 IC

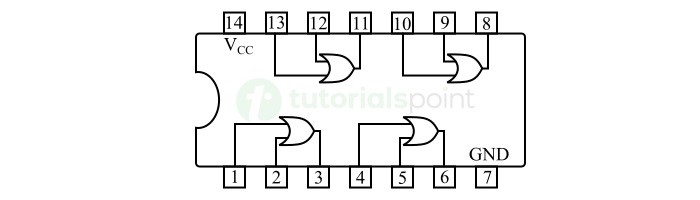

实际上,或门以集成电路或 IC 的形式提供。最流行的或门 IC 是 IC 7432,它是四路 2 输入或门 IC。它有四个两输入或门。

下图描述了或门 IC 7432 的引脚和框图。

或门 IC 7432 有 14 个引脚,它是一个晶体管-晶体管逻辑 (TTL) 或门 IC。

结论

总之,或门是一个具有两条或更多条输入线和一条输出线的基本逻辑门。仅当所有输入都为低时,它才会产生低或逻辑 0 输出,否则会产生高或逻辑 1 输出。

在本章中,我们解释了或门的理论。这里,我们仅介绍了两个和三个输入的或门。但相同的理论和技术解释适用于具有任意数量输入的或门。