数字电路 - 计数器

在前两章中,我们讨论了各种移位寄存器和使用 D 触发器的计数器。现在,让我们讨论使用 T 触发器的各种计数器。我们知道 T 触发器会在时钟信号的每个正沿或时钟信号的负沿切换输出。

"N"位二进制计数器由"N"个 T 触发器组成。如果计数器从 0 计数到 2𝑁 − 1,则它称为二进制向上计数器。同样,如果计数器从 2𝑁 − 向下计数1 变为 0,则称为二进制减法计数器。

根据触发器是否同步连接,有两种计数器。

- 异步计数器

- 同步计数器

异步计数器

如果触发器不接收相同的时钟信号,则该计数器称为异步计数器。系统时钟的输出仅作为时钟信号应用于第一个触发器。其余触发器从其前一级触发器的输出接收时钟信号。因此,所有触发器的输出不会同时改变(影响)。

现在,让我们逐一讨论以下两个计数器。

- 异步二进制上升计数器

- 异步二进制下降计数器

异步二进制上升计数器

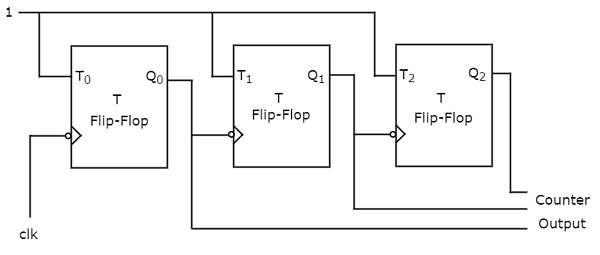

一个'N'位异步二进制上升计数器由'N'个T触发器组成。它从 0 计数到 2𝑁 − 1。下图显示了 3 位异步二进制上升计数器的框图。

3 位异步二进制上升计数器包含三个 T 触发器,所有触发器的 T 输入都连接到"1"。所有这些触发器都是负边沿触发的,但输出异步变化。时钟信号直接应用于第一个 T 触发器。因此,第一个 T 触发器的输出在时钟信号的每个负边沿切换。

第一个 T 触发器的输出用作第二个 T 触发器的时钟信号。因此,第二个 T 触发器的输出会在第一个 T 触发器输出的每个负沿切换。类似地,第三个 T 触发器的输出会在第二个 T 触发器输出的每个负沿切换,因为第二个 T 触发器的输出充当第三个 T 触发器的时钟信号。

假设从最右到最左的 T 触发器的初始状态为 $Q_{2}Q_{1}Q_{0}=000$。这里,$Q_{2}$ & $Q_{0}$ 分别是 MSB 和 LSB。我们可以从下表中了解 3 位异步二进制计数器的工作原理。

| 时钟下降沿数量 | Q0(LSB) | Q1 | Q2(MSB) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 |

| 2 | 0 | 1 | 0 |

| 3 | 1 | 1 | 0 |

| 4 | 0 | 0 | 1 |

| 5 | 1 | 0 | 1 |

| 6 | 0 | 1 | 1 |

| 7 | 1 | 1 | 1 |

此处,$Q_{0}$ 在每个时钟信号负沿处切换。$Q_{1}$ 在每个 $Q_{0}$ 从 1 变为 0 处切换,否则保持先前状态。类似地,$Q_{2}$ 在每个 $Q_{1}$ 从 1 变为 0 处切换,否则保持先前状态。

在没有时钟信号的情况下,T 触发器的初始状态为 $Q_{2}Q_{1}Q_{0}=000$。时钟信号的每个负沿处加一,并在时钟信号的第 7 个负沿处达到最大值。当施加更多时钟信号的负沿时,此模式重复。

异步二进制递减计数器

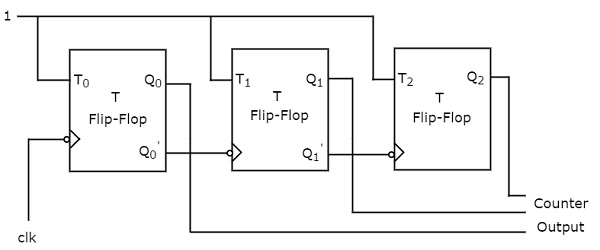

"N"位异步二进制递减计数器由"N"个 T 触发器组成。它从 2𝑁 − 1 计数到 0。下图显示了 3 位异步二进制减法计数器的框图。

3 位异步二进制减法计数器的框图与 3 位异步二进制加法计数器的框图相似。但是,唯一的区别是,不是将一级触发器的正常输出连接为下一级触发器的时钟信号,而是将一级触发器的互补输出连接为下一级触发器的时钟信号。补码输出从 1 到 0 与正常输出从 0 到 1 相同。

假设 T 触发器从最右到最左的初始状态为 $Q_{2}Q_{1}Q_{0}=000$。其中,$Q_{2}$ & $Q_{0}$ 分别为 MSB 和 LSB。我们可以从下表中了解3位异步二进制递减计数器的工作原理。

| 时钟下降沿数量 | Q0(LSB) | Q1 | Q2(MSB) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 |

| 2 | 0 | 1 | 1 |

| 3 | 1 | 0 | 1 |

| 4 | 0 | 0 | 1 |

| 5 | 1 | 1 | 0 |

| 6 | 0 | 1 | 0 |

| 7 | 1 | 0 | 0 |

此处,$Q_{0}$ 在每个时钟信号负沿处切换。$Q_{1}$ 在每个 $Q_{0}$ 从 0 变为 1 处切换,否则保持先前状态。类似地,$Q_{2}$ 在每个 $Q_{1}$ 从 0 变为 1 处切换,否则保持先前状态。

在没有时钟信号的情况下,T 触发器的初始状态为 $Q_{2}Q_{1}Q_{0}=000$。该状态在每个时钟信号负沿处减一,并在时钟信号第 8 个负沿处达到相同值。当施加更多时钟信号负沿时,此模式会重复。

同步计数器

如果所有触发器都接收相同的时钟信号,则该计数器称为同步计数器。因此,所有触发器的输出都会同时改变(影响)。

现在,让我们逐一讨论以下两个计数器。

- 同步二进制上升计数器

- 同步二进制下降计数器

同步二进制上升计数器

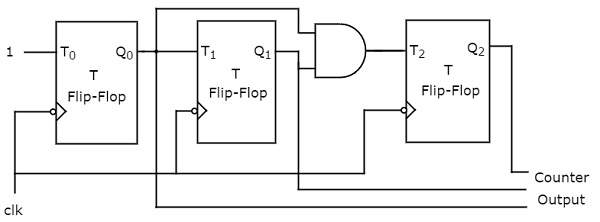

"N"位同步二进制上升计数器由"N"个 T 触发器组成。它从 0 计数到 2𝑁 − 1。下图显示了 3 位同步二进制上升计数器的框图。

3 位同步二进制上升计数器包含三个 T 触发器 &一个 2 输入与门。所有这些触发器都是负沿触发的,触发器的输出同步变化(影响)。第一、第二和第三个触发器的 T 输入分别为 1、$Q_{0}$ 和 $Q_{1}Q_{0}$。

第一个 T 触发器的输出在时钟信号的每个负沿切换。如果 $Q_{0}$ 为 1,则第二个 T 触发器的输出在时钟信号的每个负沿切换。如果 $Q_{0}$ 和 $Q_{1}$ 均为 1,则第三个 T 触发器的输出在时钟信号的每个负沿切换。

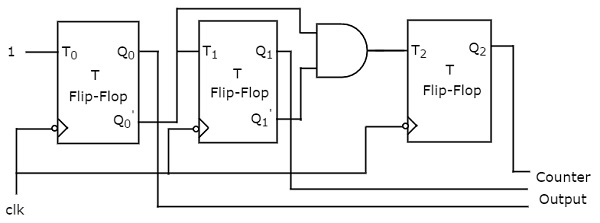

同步二进制递减计数器

"N"位同步二进制递减计数器由"N"个 T 触发器组成。它从 2𝑁 − 1 计数到 0。下图显示了 3 位同步二进制减法计数器的框图。

3 位同步二进制减法计数器包含三个 T 触发器和一个 2 输入与门。所有这些触发器都是负沿触发的,触发器的输出同步变化(影响)。第一、第二和第三个触发器的 T 输入分别为 1、${Q_{0}}'$ &' ${Q_{1}}'$${Q_{0}}'$。

第一个 T 触发器的输出在时钟信号的每个负沿切换。如果 ${Q_{0}}'$ 为 1,则第二个 T 触发器的输出会在时钟信号的每个负沿切换。如果 ${Q_{1}}'$ 和 ${Q_{0}}'$ 均为 1,则第三个 T 触发器的输出会在时钟信号的每个负沿切换。