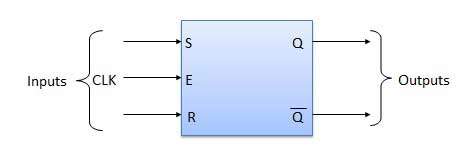

顺序电路

组合电路不使用任何内存。因此,输入的先前状态对电路的当前状态没有任何影响。但顺序电路具有内存,因此输出可以根据输入而变化。这种类型的电路使用先前的输入、输出、时钟和内存元件。

框图

触发器

触发器是一种顺序电路,它通常仅在特定时刻采样其输入并改变其输出,而不是连续地采样。触发器被称为边缘敏感或边缘触发,而不是像锁存器那样由电平触发。

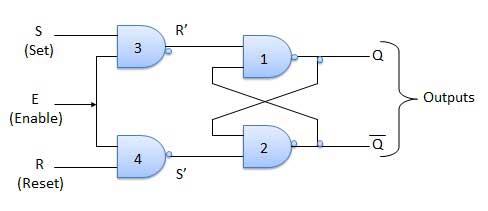

S-R 触发器

它基本上是使用 NAND 门的 S-R 锁存器,并带有额外的 启用 输入。它也被称为电平触发 SR-FF。为此,当且仅当启用输入 (E) 处于活动状态时,输出中的电路才会发生。简而言之,如果 E = 1,该电路将作为 S-R 锁存器运行,但如果 E = 0,则输出不会发生变化。

框图

电路图

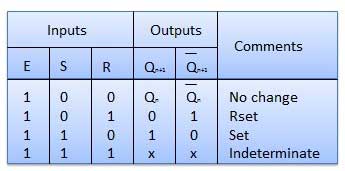

真值表

操作

| S.N. | 条件 | 操作 |

|---|---|---|

| 1 | S = R = 0 : 无变化 |

如果 S = R = 0,则 NAND 门 3 和 4 的输出被强制变为 1。 因此 R' 和 S' 都等于 1。由于 S' 和 R' 是使用 NAND 门的基本 S-R 锁存器的输入,因此输出状态不会发生变化。 |

| 2 | S = 0,R = 1,E = 1 |

由于 S = 0,NAND-3 的输出,即 R' = 1 和 E = 1,输出NAND-4 即 S' = 0。 因此 Qn+1 = 0 且 Qn+1 bar = 1。这是复位条件。 |

| 3 | S = 1, R = 0, E = 1 |

NAND-3 的输出即 R' = 0 且 NAND-4 的输出即 S' = 1。 因此 S-R NAND 锁存器的输出为 Qn+1 = 1 且 Qn+1 bar = 0。这是复位条件。 |

| 4 | S = 1, R = 1,E = 1 |

由于 S = 1、R = 1 和 E = 1,NAND 门 3 和 4 的输出均为 0,即 S' = R' = 0。 因此,基本 NAND 锁存器中将出现 竞争 情况。 |

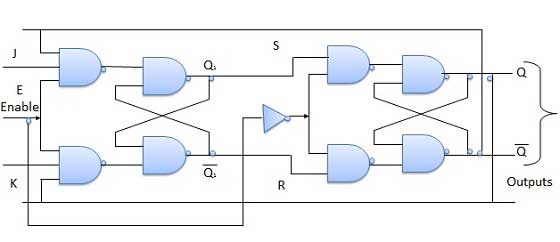

主从 JK 触发器

主从 JK 触发器是两个 S-R FF 的级联,其反馈来自第二个触发器的输出到第一个触发器的输入。主触发器是正电平触发的。但由于时钟线中存在反相器,从触发器将对负电平做出响应。因此,当时钟 = 1(正电平)时,主触发器处于活动状态,从触发器处于非活动状态。而当时钟 = 0(低电平)时,从设备处于活动状态,主设备处于非活动状态。

电路图

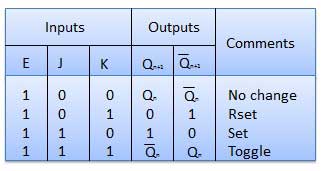

真值表

操作

| S.N. | 条件 | 操作 |

|---|---|---|

| 1 | J = K = 0(无变化) |

当时钟 = 0 时,从设备变为活动状态,主设备处于非活动状态。但由于 S 和 R 输入没有变化,从设备输出也将保持不变。因此,如果 J = K =0,则输出不会改变。 |

| 2 | J = 0 和 K = 1(重置) |

时钟 = 1 − 主设备激活,从设备未激活。因此主设备的输出变为 Q1 = 0 和 Q1 bar = 1。这意味着 S = 0 和 R =1。 时钟 = 0 − 从设备激活,主设备未激活。因此从设备的输出变为 Q = 0 和 Q bar = 1。 再次,时钟 = 1 − 主设备激活,从设备未激活。因此,即使将改变的输出 Q = 0 和 Q bar = 1 反馈给主机,其输出仍为 Q1 = 0 和 Q1 bar = 1。这意味着 S = 0 和 R = 1。 因此,当时钟 = 0 且从机变为活动状态时,从机的输出将保持 Q = 0 和 Q bar = 1。这样,我们就可以从主从机获得稳定的输出。 |

| 3 | J = 1 和 K = 0(设置) |

时钟 = 1 − 主机活动,从机不活动。因此,主机的输出变为 Q1 = 1 和 Q1 bar = 0。这意味着 S = 1 和 R =0。 时钟 = 0 − 从机活动,主机不活动。因此,从设备的输出变为 Q = 1 和 Q bar = 0。 再次,时钟 = 1 −,然后可以显示从设备的输出稳定为 Q = 1 和 Q bar = 0。 |

| 4 | J = K = 1(切换) |

时钟 = 1 − 主设备处于活动状态,从设备处于非活动状态。主设备的输出将切换。因此 S 和 R 也将被反转。 时钟 = 0 − 从设备处于活动状态,主设备处于非活动状态。从设备的输出将切换。 这些更改的输出将返回到主设备输入。但由于时钟 = 0,主设备仍处于非活动状态。因此它不会响应这些更改的输出。这避免了导致竞争条件的多次切换。主从触发器将避免竞争情况。 |

延迟触发器/D 触发器

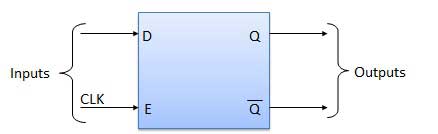

延迟触发器或 D 触发器是简单的门控 S-R 锁存器,在 S 和 R 输入之间连接一个 NAND 反相器。它只有一个输入。输入数据会在一段时间后出现在输出端。由于 i/p 和 o/p 之间的数据延迟,它被称为延迟触发器。由于 NAND 反相器,S 和 R 将是彼此的互补。因此,S = R = 0 或 S = R = 1,这些输入条件永远不会出现。 SR = 00 和 SR = 1 条件可避免此问题。

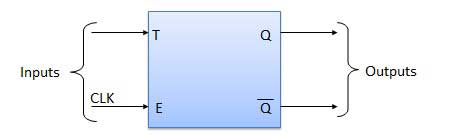

框图

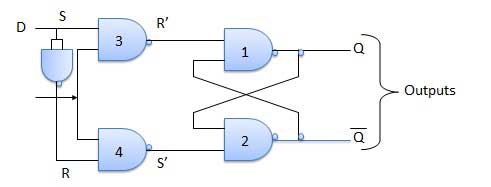

电路图

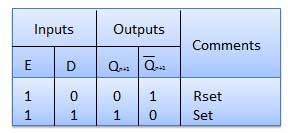

真值表

操作

| S.N. | 条件 | 操作 |

|---|---|---|

| 1 | E = 0 |

锁存器已禁用。因此输出没有变化。 |

| 2 | E = 1 且 D = 0 |

如果 E = 1 且 D = 0,则 S = 0 且 R = 1。因此,无论当前状态如何,下一个状态都是 Qn+1 = 0 且 Qn+1 bar = 1。这是重置条件。 |

| 3 | E = 1 且 D = 1 |

如果 E = 1 且 D = 1,则 S = 1 且 R = 0。这将设置锁存器,并且 Qn+1 = 1 且 Qn+1 bar = 0,而不管当前状态如何。 |

切换触发器/T 触发器

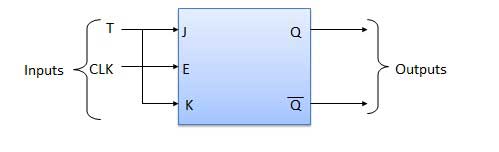

切换触发器基本上是 JK 触发器,J 和 K 端子永久连接在一起。它只有用 T 表示的输入,如符号图所示。正边沿触发 T 触发器的符号显示在框图中。

符号图

框图

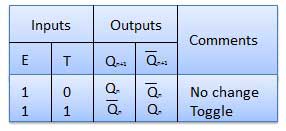

真值表

操作

| S.N. | 条件 | 操作 |

|---|---|---|

| 1 | T = 0, J = K = 0 | 输出 Q 和 Q bar 不会改变 |

| 2 | T = 1, J = K = 1 | 输出将根据时钟信号的每个前沿切换。 |