锁相环 IC

锁相环(PLL)是线性系统中至关重要的模块之一。它在雷达、卫星、FM 等通信系统中很有用。

本章详细讨论了 PLL 和 IC 565 的框图。

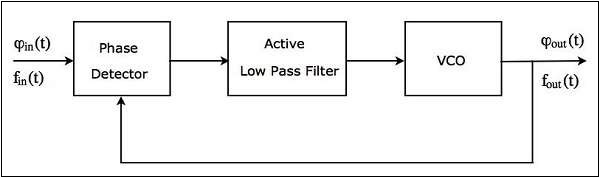

PLL 的框图

锁相环 (PLL) 主要由以下三个块组成 −

- 相位检测器

- 有源低通滤波器

- 压控振荡器 (VCO)

PLL 的框图如下图所示 −

相位检测器的输出用作输入有源低通滤波器。类似地,有源低通滤波器的输出用作 VCO 的输入。

PLL 的工作如下 −

相位检测器产生直流电压,该电压与频率为 $f_{in}$ 的输入信号和频率为 $f_{out}$ 的反馈(输出)信号之间的相位差成比例。

相位检测器是一个乘法器,它在其输出端产生两个频率分量 − 频率 $f_{in}$ 和 $f_{out}$ 之和以及频率 $f_{in}$ 和 $f_{out}$ 之差。

有源低通滤波器在消除相位检测器输出中存在的高频分量后,在其输出端产生直流电压。它还会放大信号。

当没有输入时,VCO 会产生具有特定频率的信号。通过向其施加直流电压,可以将此频率移至任一侧。因此,频率偏差与低通滤波器输出端的直流电压成正比。

上述操作一直进行,直到 VCO 频率等于输入信号频率。根据应用类型,我们可以使用有源低通滤波器的输出或 VCO 的输出。 PLL 用于许多应用,例如 FM 解调器、时钟发生器等。

PLL 以以下三种模式之一运行 −

- 自由运行模式

- 捕获模式

- 锁定模式

最初,当没有输入时,PLL 以自由运行模式运行。当将具有某个频率的输入信号施加到 PLL 时,VCO 的输出信号频率将开始变化。在此阶段,PLL 被称为以捕获模式运行。VCO 的输出信号频率将不断变化,直到等于输入信号频率。现在,据说 PLL 正在 锁定模式 下运行。

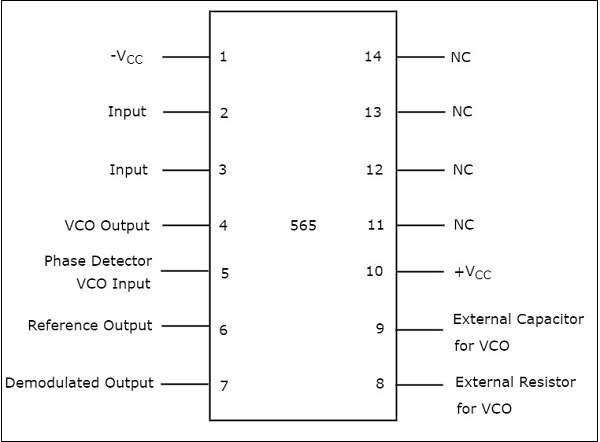

IC 565

IC 565 是最常用的锁相环 IC。它是一种 14 针双列直插式封装 (DIP)。IC 565 的 引脚图 如下图所示 −

从上图可以看出,每个引脚的用途不言而喻。在 14 个引脚中,只有 10 个引脚(引脚编号 1 至 10)用于 PLL 的运行。因此,剩余的 4 个引脚(引脚编号 11 至 14)标有 NC(无连接)。

当引脚编号 2 和 3 接地时,VCO 会在 IC 565 的引脚编号 4 处产生输出。从数学上讲,我们可以将 VCO 的输出频率 $f_{out}$ 写为。

$$f_{out}=\frac{0.25}{R_VC_V}$$

其中,

$R_{V}$ 是连接到引脚 8 的外部电阻

$C_{V}$ 是连接到引脚 9 的外部电容

通过选择适当的 $R_{V}$ 和 $C_{V}$ 值,我们可以确定 VCO 的输出频率 $f_{out}$。

引脚 4 和 5要用外部电线短接,以便 VCO 的输出可以用作相位检测器的输入之一。

IC 565 的内部电阻为 $3.6K\Omega$。必须在引脚 7 和 10 之间连接一个电容器 C,以便制作具有该内部电阻的低通滤波器。

请注意,根据要求,我们必须正确配置 IC 565 的引脚。