VLSI 设计 - 顺序 MOS 逻辑电路

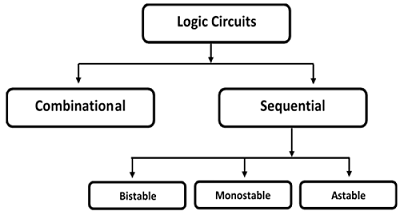

逻辑电路分为两类 − (a) 组合电路和 (b) 顺序电路。

在组合电路中,输出仅取决于最新输入的条件。

在顺序电路中,输出不仅取决于最新输入,还取决于先前输入的条件。顺序电路包含存储元件。

顺序电路有三种类型 −

双稳态 − 双稳态电路有两个稳定的工作点,将处于任一状态。示例 −存储单元、锁存器、触发器和寄存器。

单稳态 − 单稳态电路只有一个稳定的工作点,即使它们暂时被扰动到相反的状态,它们也会及时返回到其稳定的工作点。示例:定时器、脉冲发生器。

非稳态 − 电路没有稳定的工作点,并且在几个状态之间振荡。示例 −环形振荡器。

CMOS 逻辑电路

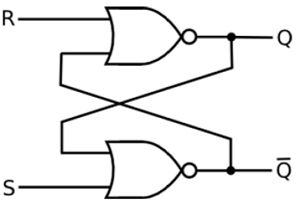

基于 NOR 门的 SR 锁存器

如果设置输入 (S) 等于逻辑 "1" 且重置输入等于逻辑 "0"。 则输出 Q 将被强制为逻辑 "1"。而 $\overline{Q}$ 则被强制为逻辑 "0"。这意味着 SR 锁存器将被设置,而不管其先前的状态如何。

类似地,如果 S 等于"0"且 R 等于 "1" 则输出 Q 将被强制为 "0" 而 $\overline{Q}$ 则被强制为 "1"。这意味着锁存器被重置,无论其先前保持的状态如何。最后,如果输入 S 和 R 都等于逻辑 "1",则两个输出都将被强制为逻辑 "0",这与 Q 和 $\overline{Q}$ 的互补性相冲突。

因此,在正常运行期间不允许这种输入组合。表中给出了基于 NOR 的 SR 锁存器的真值表。

| S | R | Q | $\overline{Q}$ | 操作 |

|---|---|---|---|---|

| 0 | 0 | Q | $\overline{Q}$ | 保持 |

| 1 | 0 | 1 | 0 | 设置 |

| 0 | 1 | 0 | 1 | 重置 |

| 1 | 1 | 0 | 0 | 不允许 |

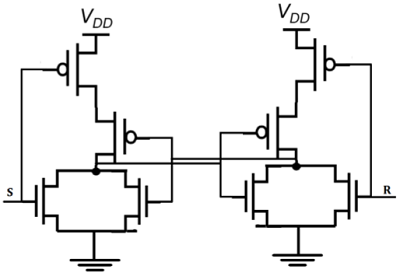

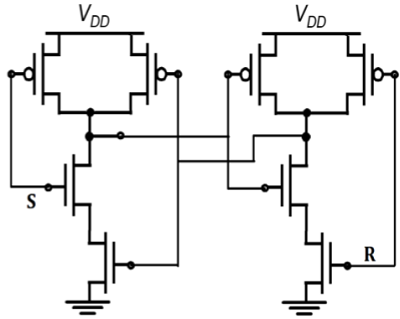

下图所示为基于 NOR 门的 CMOS SR 闩锁。

如果 S 等于 VOH,R 等于 VOL,则并联连接的晶体管 M1 和 M2 均将导通。节点$\overline{Q}$上的电压将呈现逻辑低电平VOL = 0。

同时,M3和M4均关闭,导致节点Q上的逻辑高电压VOH。如果R等于VOH且S等于VOL,则M1和M2关闭,M3和M4打开。

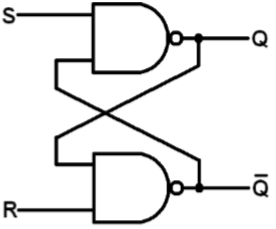

基于NAND门的SR锁存器

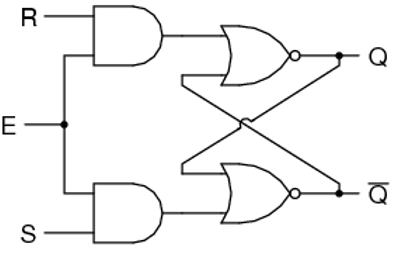

图中显示了基于NAND的SR锁存器的框图和门级示意图。S和R输入端的小圆圈表示电路响应低电平有效输入信号。基于 NAND 的 SR 锁存器的真值表如表所示

| S | R | Q | Q′ | |

| 0 | 0 | NC | NC | 无变化。闩锁保持当前状态。 |

| 1 | 0 | 1 | 0 | 闩锁已设置。 |

| 0 | 1 | 0 | 1 | 闩锁已重置。 |

| 1 | 1 | 0 | 0 | 无效条件。 |

如果 S 变为 0(而 R = 1),Q 变为高电平,将 $\overline{Q}$ 拉低,锁存器进入设置状态

S = 0 则 Q = 1(如果 R = 1)

如果 R 变为 0(而 S = 1),Q 变为高电平,将 $\overline{Q}$ 拉低,锁存器复位

R = 0 则 Q = 1(如果 S = 1)

保持状态要求 S 和 R 都为高电平。如果 S = R = 0,则不允许输出,因为这会导致不确定的状态。基于 NAND 门的 CMOS SR 锁存器如图所示。

基于 NAND 门的耗尽负载 nMOS SR 锁存器如图所示。其操作与 CMOS NAND SR 锁存器类似。CMOS 电路实现具有较低的静态功耗和较高的噪声容限。

CMOS 逻辑电路

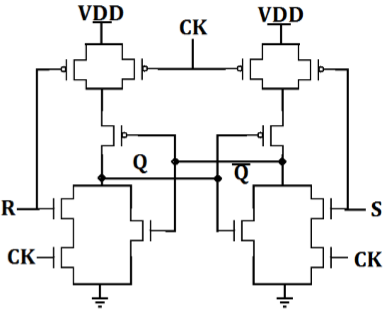

时钟 SR 锁存器

该图显示了一个基于 NOR 的 SR 锁存器,其中添加了一个时钟。仅当 CLK 为高电平时,锁存器才会对输入 S 和 R 做出响应。

当 CLK 为低电平时,锁存器会保持其当前状态。观察 Q 是否改变状态 −

- 当 S 在正 CLK 期间变为高电平时。

- 在 CLK 低电平期间 S 和 R 发生变化后,在 CLK 上升沿上。

- CLK 为高电平时,S 中出现正向毛刺

- 当 R 在正 CLK 期间变为高电平时。

图中显示了基于时钟 NOR 的 SR 锁存器的 CMOS AOI 实现。请注意,只需要 12 个晶体管。

当 CLK 为低时,N 树 N 中的两个串联端子处于打开状态,而树 P 中的两个并联晶体管处于打开状态,从而将状态保留在存储单元中。

当时钟为高时,电路变为简单的基于 NOR 的 CMOS 锁存器,它将响应输入 S 和 R。

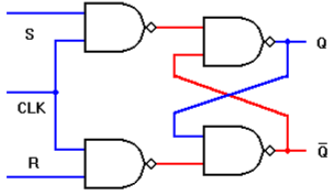

基于 NAND 门的时钟 SR 锁存器

电路由四个 NAND 门实现。如果该电路采用 CMOS 实现,则需要 16 个晶体管。

- 仅当 CLK 为高电平时,锁存器才会对 S 或 R 做出响应。

- 如果输入信号和 CLK 信号均为高电平有效:即,当 CLK ="1"、S ="1"和 R ="0"时,将设置锁存器输出 Q

- 类似地,当 CLK ="1"、"S ="0"和 时,将重置锁存器。

当 CLK 为低电平时,锁存器将保持其当前状态。

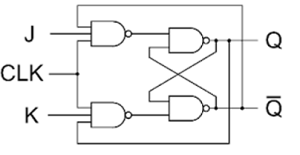

时钟 JK 锁存器

上图显示了基于 NAND 门的时钟 JK 锁存器。 SR 锁存器的缺点是,当 S 和 R 都为高电平时,其输出状态变得不确定。JK 锁存器通过使用从输出到输入的反馈来消除此问题,这样真值表的所有输入状态都是允许的。如果 J = K = 0,锁存器将保持其当前状态。

如果 J = 1 且 K = 0,锁存器将在下一个正向时钟沿设置,即 Q = 1,$\overline{Q}$ = 0

如果 J = 0 且 K = 1,锁存器将在下一个正向时钟沿重置,即 Q = 1 且 $\overline{Q}$ = 0。

如果 J = K = 1,锁存器将在下一个正向时钟沿切换

表中给出的真值表总结了时钟 JK 锁存器的操作。

J |

K |

Q |

$\overline{Q}$ | S |

R |

Q |

$\overline{Q}$ | 操作 |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | Hold |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | Reset |

| 1 | 0 | 1 | 0 | 0 | 1 | |||

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | Set |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | toggle |

| 1 | 0 | 1 | 0 | 0 | 1 |

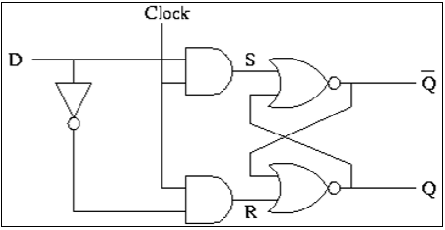

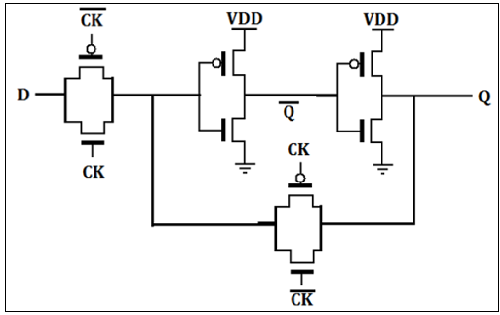

CMOS D 锁存器实现

D 锁存器通常采用传输门 (TG) 开关实现,如图所示。输入 TG 由 CLK 激活,而锁存器反馈环路 TG 由 CLK 激活。当 CLK 为高电平时,输入 D 被接受。当 CLK 变为低电平时,输入开路,锁存器由先前的数据 D 设置。