VLSI 设计 - FPGA 技术

FPGA – 简介

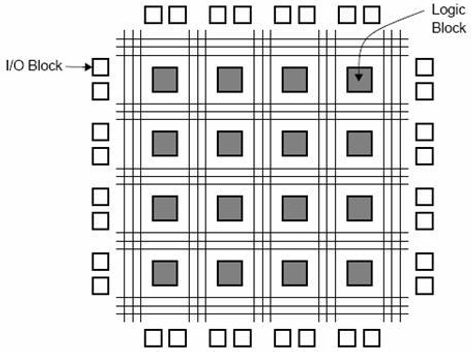

FPGA 的全称是"现场可编程门阵列"。它包含一万到一百万个逻辑门,并带有可编程互连。可编程互连可供用户或设计人员轻松执行给定功能。图中显示了一个典型的 FPGA 芯片模型。它有 I/O 块,这些块根据功能进行设计和编号。对于每个逻辑级组成的模块,都有CLB(可配置逻辑块)。

CLB 执行给定模块的逻辑操作。CLB 和 I/O 块之间的互连是借助水平布线通道、垂直布线通道和 PSM(可编程多路复用器)实现的。

它包含的 CLB 数量仅决定了 FPGA 的复杂性。 CLB 和 PSM 的功能由 VHDL 或任何其他硬件描述语言设计。编程后,CLB 和 PSM 被放置在芯片上并通过路由通道相互连接。

优点

- 从设计过程到功能芯片所需的时间非常短。

- 不涉及任何物理制造步骤。

- 唯一的缺点是,它比其他样式更昂贵。

门阵列设计

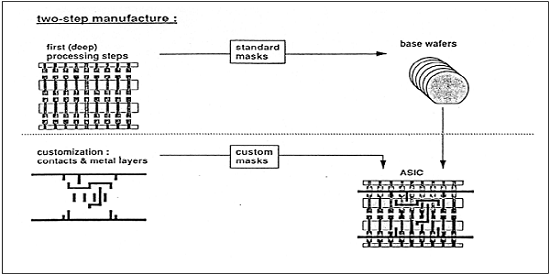

在快速原型设计能力方面,门阵列 (GA) 仅次于 FPGA。虽然用户编程对于 FPGA 芯片的设计实现很重要,但 GA 使用金属掩模设计和处理。门阵列实现需要两步制造过程。

第一阶段会在每个 GA 芯片上产生一个未指定晶体管阵列。这些未指定芯片可以存储起来以供以后定制,定制过程通过定义阵列晶体管之间的金属互连来完成。金属互连的图案化是在芯片制造过程结束时完成的,因此周转时间仍然可以很短,几天到几周。下图显示了门阵列实现的基本处理步骤。

典型的门阵列平台使用称为通道的专用区域,用于 MOS 晶体管行或列之间的单元间路由。它们简化了互连。执行基本逻辑门的互连模式存储在库中,然后可以根据网络表使用该库定制未提交晶体管的行。

在大多数现代 GA 中,多个金属层用于通道布线。通过使用多个互连层,可以在有源单元区域上实现布线;这样就可以像在 Sea-of-Gates (SOG) 芯片中一样移除布线通道。在这里,整个芯片表面都覆盖着未提交的 nMOS 和 pMOS 晶体管。可以使用金属掩模定制相邻的晶体管以形成基本逻辑门。

对于单元间布线,必须牺牲一些未提交的晶体管。这种设计风格为互连提供了更大的灵活性,并且通常密度更高。GA 芯片利用率是通过使用的芯片面积除以总芯片面积来衡量的。它比 FPGA 更高,芯片速度也更高。

基于标准单元的设计

基于标准单元的设计需要开发完整的自定义掩模集。标准单元也称为多单元。在这种方法中,所有常用的逻辑单元都经过开发、特性化并存储在标准单元库中。

库可能包含几百个单元,包括反相器、NAND 门、NOR 门、复杂 AOI、OAI 门、D 锁存器和触发器。每种门类型都可以实现多个版本,以提供足够的驱动能力来满足不同的扇出要求。反相门可以具有标准尺寸、双倍尺寸和四倍尺寸,以便芯片设计人员可以选择适当的尺寸以获得高电路速度和布局密度。

每个单元都根据几种不同的特性类别进行表征,例如,

- 延迟时间与负载电容

- 电路仿真模型

- 时序仿真模型

- 故障仿真模型

- 用于布局布线的单元数据

- 掩模数据

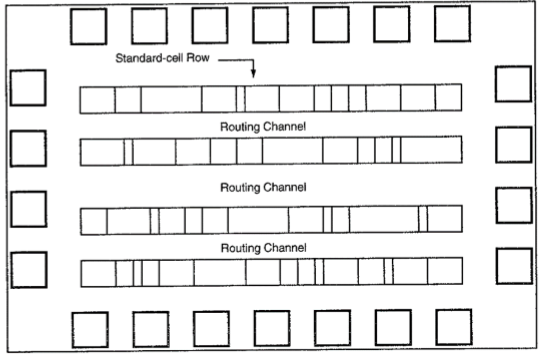

为了实现单元的自动放置和布线,每个单元布局都设计有固定高度,以便多个单元可以并排排列以形成行。电源和接地导轨与单元的上下边界平行。因此,相邻单元共享一个公共电源总线和一个公共接地总线。下图显示的是基于标准单元的设计的平面图。

全定制设计

在全定制设计中,整个掩模设计都是全新的,无需使用任何库。这种设计风格的开发成本正在上升。因此,设计重用的概念越来越流行,可以减少设计周期和开发成本。

最难的全定制设计可能是存储单元的设计,无论是静态的还是动态的。对于逻辑芯片设计,在同一芯片上结合使用不同的设计风格(即标准单元、数据路径单元和可编程逻辑阵列 (PLA))可获得良好的协商效果。

实际上,设计师会进行完全自定义布局,即每个晶体管的几何形状、方向和位置。设计效率通常很低;通常每个设计师每天只能设计几十个晶体管。在数字 CMOS VLSI 中,由于劳动力成本高昂,几乎不使用完全自定义设计。这些设计风格包括大批量产品的设计,例如内存芯片、高性能微处理器和 FPGA。