VLSI 设计 - 数字系统

超大规模集成 (VLSI) 是通过将数千个 晶体管 组合到单个芯片中来创建 集成电路 (IC) 的过程。VLSI 始于 20 世纪 70 年代,当时正在开发复杂的 半导体 和 通信 技术。微处理器 是一种 VLSI 设备。

在引入 VLSI 技术之前,大多数 IC 可以执行的功能有限。电子电路可能由 CPU、ROM、RAM 和其他 胶合逻辑 组成。VLSI 允许 IC 设计人员将所有这些添加到一个芯片中。

电子行业在过去几十年中实现了惊人的增长,这主要归功于大规模集成技术和系统设计应用的快速发展。随着超大规模集成 (VLSI) 设计的出现,集成电路 (IC) 在高性能计算、控制、电信、图像和视频处理以及消费电子产品中的应用数量正在快速增长。

当前的尖端技术(例如高分辨率和低比特率视频和蜂窝通信)为最终用户提供了大量应用、处理能力和便携性。预计这一趋势将迅速增长,对 VLSI 设计和系统设计具有非常重要的意义。

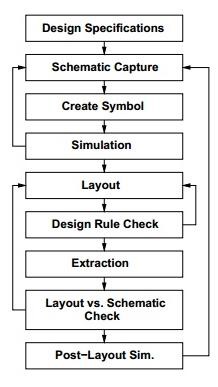

VLSI 设计流程

VLSI IC 电路设计流程如下图所示。设计的各个层次都已编号,而块则显示了设计流程中的过程。

首先是规范,它们抽象地描述了要设计的数字 IC 电路的功能、接口和架构。

然后创建行为描述,以从功能、性能、对给定标准的符合性和其他规范的角度分析设计。

RTL 描述是使用 HDL 完成的。此 RTL 描述经过模拟以测试功能。从这里开始,我们需要 EDA 工具的帮助。

然后使用逻辑综合工具将 RTL 描述转换为门级网表。门级网表是对门及其之间连接的电路描述,这些门的制作方式符合时序、功率和面积规范。

最后,进行物理布局,验证后送去制造。

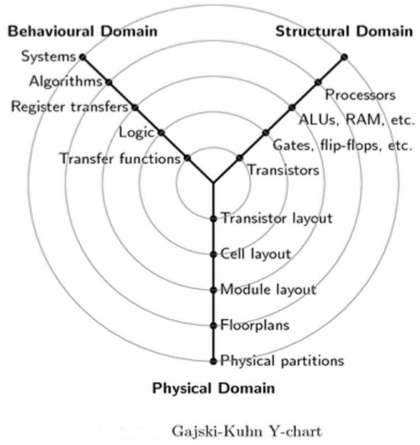

Y 图

Gajski-Kuhn Y 图是一个模型,它捕捉了设计半导体器件时的考虑因素。

Gajski-Kuhn Y 图的三个域位于径向轴上。每个域都可以使用同心环划分为抽象级别。

在顶层(外环),我们考虑芯片的架构;在较低层次(内环),我们逐步将设计细化为更精细的详细实现 −

通过高级综合或逻辑综合的过程,可以从行为描述创建结构描述。

通过布局综合,可以从结构描述创建物理描述。

设计层次结构

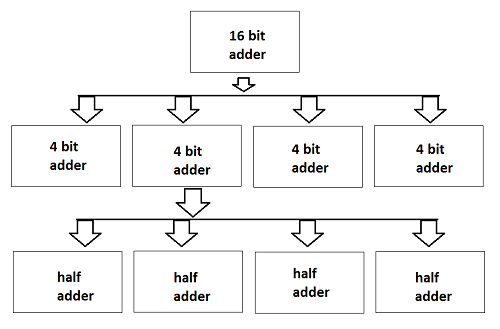

设计层次涉及"分而治之"的原则。它只不过是将任务划分为更小的任务,直到达到最简单的级别。这个过程是最合适的,因为设计的最后演变变得如此简单,以至于制造变得更容易。

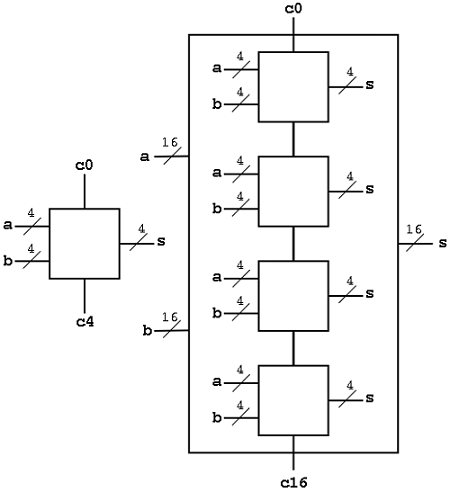

我们可以将给定的任务设计到设计流程的领域(行为、结构和几何)。为了理解这一点,我们以设计一个 16 位加法器为例,如下图所示。

这里,整个 16 位加法器芯片被分成四个 4 位加法器模块。进一步,将 4 位加法器分为 1 位加法器或半加法器。1 位加法是最简单的设计过程,其内部电路也易于在芯片上制造。现在,连接所有最后四个加法器,我们可以设计一个 4 位加法器,继续,我们可以设计一个 16 位加法器。