组合 MOS 逻辑电路

组合逻辑电路或门对多个输入变量执行布尔运算,并将输出确定为输入的布尔函数,是所有数字系统的基本构建块。我们将研究简单的电路配置,例如双输入 NAND 和 NOR 门,然后将我们的分析扩展到更一般的多输入电路结构情况。

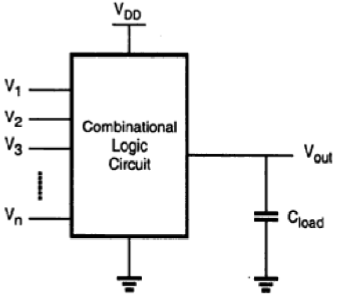

接下来,将以类似的方式介绍 CMOS 逻辑电路。我们将强调 nMOS 耗尽负载逻辑和 CMOS 逻辑电路之间的相似之处和不同之处,并通过示例指出 CMOS 门的优势。在其最一般的形式中,执行布尔函数的组合逻辑电路或门可以表示为多输入、单输出系统,如图所示。

以地电位为参考的节点电压表示所有输入变量。使用正逻辑约定,布尔(或逻辑)值"1"可以用高电压 VDD 表示,布尔(或逻辑)值"0"可以用低电压 0 表示。输出节点加载电容 CL,该电容表示电路中寄生器件的组合电容。

CMOS 逻辑电路

CMOS 双输入 NOR 门

该电路由并联 n-net 和串联互补 p-net 组成。输入电压 VX 和 VY 施加到一个 nMOS 和一个 pMOS 晶体管的栅极。

当一个或两个输入为高电平时,即当 n-net 在输出节点和地之间创建导电路径时,p-net 被切断。如果两个输入电压都较低,即 n-net 截止,则 p-net 会在输出节点和电源电压之间创建一条导电路径。

对于任何给定的输入组合,互补电路结构是这样的,输出通过低电阻路径连接到 VDD 或接地,并且对于任何输入组合,VDD 和接地之间均不建立直流电流路径。CMOS 双输入 NOR 门的输出电压将获得逻辑低电压 VOL = 0 和逻辑高电压 VOH = VDD。开关阈值电压 Vth 的公式如下

$$V_{th}\left ( NOR2 ight ) = \frac{V_{T,n}+\frac{1}{2}\sqrt{\frac{k_{p}}{k_{n}}\left ( V_{DD}-\left | V_{T,p} ight | ight )}}{1+\frac{1}{2}\sqrt{\frac{k_{p}}{k_{n}}}}$$

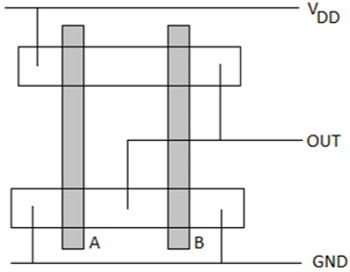

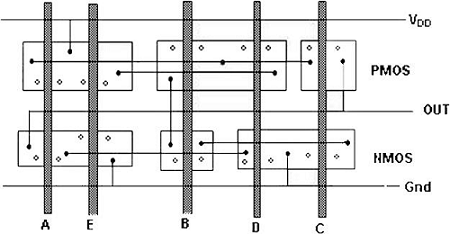

CMOS 2 输入 NOR 门的布局

该图显示了 CMOS 2 输入 NOR 门的示例布局,使用单层金属和单层多晶硅。此布局的特点是 −

- 每个输入都有一条垂直折线

- 分别为 N 和 P 器件提供单一活动形状

- 水平运行的金属总线

下图显示了 CMOS N0R2 门的棒图;它直接对应于布局,但不包含 W 和 L 信息。扩散区域用矩形表示,金属连接和实线和圆圈分别表示触点,而交叉阴影条表示多晶硅柱。棒状图对于规划最佳布局拓扑非常有用。

CMOS 双输入 NAND 门

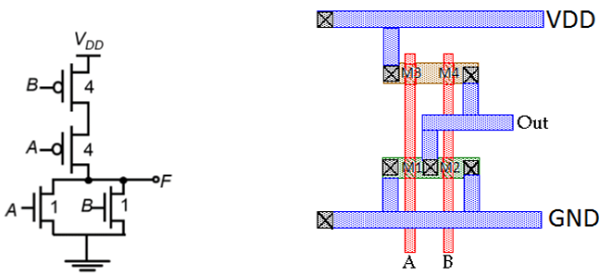

下图给出了双输入 CMOS NAND 门的电路图。

该电路的工作原理与 CMOS 双输入 NOR 操作完全相同。如果两个输入电压均为逻辑高电平,则由两个串联 nMOS 晶体管组成的 n-net 会在输出节点和地之间创建导电路径。 p-net 中并联的两个 pMOS 晶体管都将关闭。

对于所有其他输入组合,pMOS 晶体管中的一个或两个都将打开,而 p-net 被切断,从而在输出节点和电源电压之间创建电流路径。此门的开关阈值为 −

$$V_{th}\left ( NAND2 ight ) = \frac{V_{T,n}+2\sqrt{\frac{k_{p}}{k_{n}}\left ( V_{DD}-\left | V_{T,p} ight | ight )}}{1+2\sqrt{\frac{k_{p}}{k_{n}}}}$$

此布局的特点如下 −

- 用于输入的单条多晶硅线垂直穿过 N 和 P 有源区。

- 单有源形状用于构建 nMOS 器件和 pMOS 器件。

- 电源总线水平穿过布局的顶部和底部。

- 输出线水平运行,方便连接到相邻电路。

复杂逻辑电路

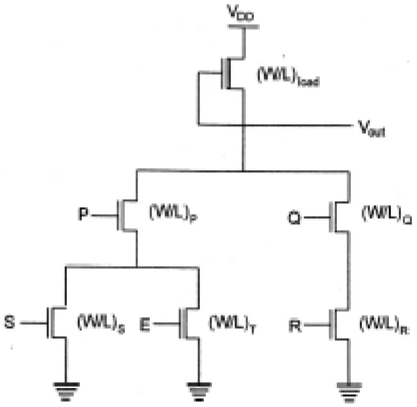

NMOS 耗尽负载复杂逻辑门

为了实现多个输入变量的复杂函数,为 NOR 和 NAND 开发的基本电路结构和设计原理可以扩展到复杂逻辑门。使用少量晶体管实现复杂逻辑功能的能力是 nMOS 和 CMOS 逻辑电路最吸引人的特性之一。以下面的布尔函数为例。

$$\overline{Z=P\left ( S+T ight )+QR}$$

用于实现该函数的 nMOS 耗尽负载复合逻辑门如图所示。在该图中,三个驱动晶体管的左侧 nMOS 驱动分支用于执行逻辑函数 P (S + T),而右侧分支执行函数 QR。通过并联连接两个分支,并将负载晶体管放置在输出节点和电源电压 VDD 之间,我们得到给定的复合函数。每个输入变量只分配给一个驱动器。

检查电路拓扑结构可得出下拉网络 − 的简单设计原则

- 或操作由并联驱动器执行。

- 与操作由串联驱动器执行。

- 反转由 MOS 电路操作的性质提供。

如果实现该功能的电路中的所有输入变量均为逻辑高,则由五个 nMOS 晶体管组成的下拉网络的等效驱动器 (W/L) 比率为

$$\frac{W}{L}=\frac{1}{\frac{1}{\left ( W/L ight )Q}+\frac{1}{\left ( W/L ight )R}}+\frac{1}{\frac{1}{\left ( W/L ight )P}+\frac{1}{\left ( W/L ight )S+\left ( W/L ight )Q}}$$

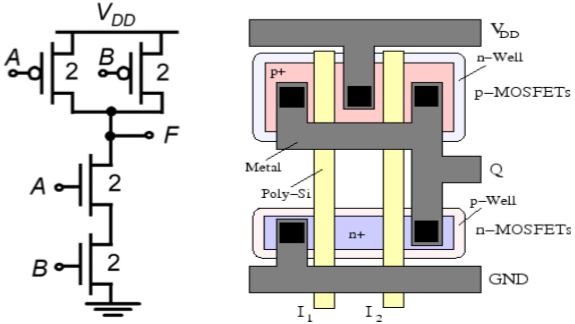

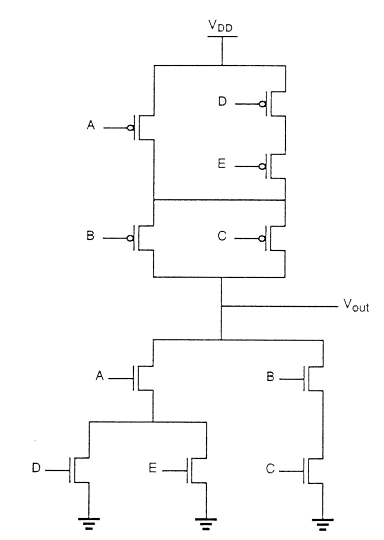

复杂 CMOS 逻辑门

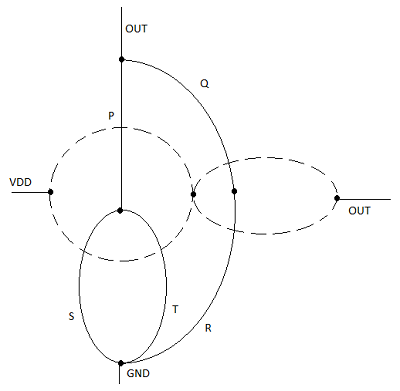

n-net 或下拉网络的实现基于与 nMOS 耗尽负载复杂逻辑门相同的基本设计原理。pMOS 上拉网络必须是 n-net 的对偶网络。

这意味着 nMOS 网络中的所有并联连接都将对应于 pMOS 网络中的串联连接,而 nMOS 网络中的所有串联连接都对应于 pMOS 网络中的并联连接。该图显示了从 n-net(下拉)图构建双 p-net(上拉)图的简单方法。

下拉网络中的每个驱动晶体管都由 ai 表示,每个节点都由下拉图中的顶点表示。接下来,在拉图中的每个受限区域内创建一个新顶点,并且相邻顶点通过仅与下拉图中每个边相交一次的边连接。这个新图显示了上拉网络。

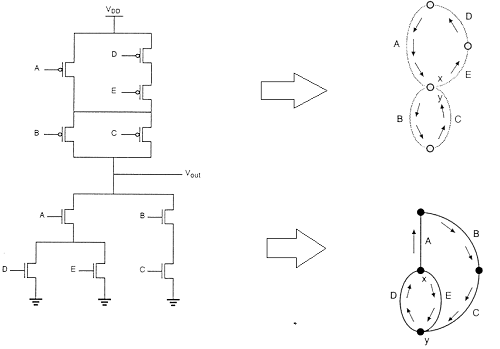

使用欧拉图方法的布局技术

该图显示了复杂函数的 CMOS 实现及其棒状图,该棒状图以任意门顺序完成,这为 CMOS 门提供了非常不理想的布局。

在这种情况下,多晶硅柱之间的分离必须允许扩散到扩散之间的分离。这肯定会消耗大量额外的硅面积。

通过使用欧拉路径,我们可以获得最佳布局。欧拉路径定义为一条不间断的路径,它恰好遍历图中的每个边(分支)一次。在输入顺序相同的下拉树图和上拉树图中查找欧拉路径。