数字电路 - 移位寄存器

我们知道一个触发器可以存储一位信息。为了存储多位信息,我们需要多个触发器。用于保存(存储)二进制数据的触发器组称为寄存器。

如果寄存器能够将位移向右侧或左侧,则称为移位寄存器。"N"位移位寄存器包含"N"个触发器。以下是基于应用输入和访问输出的四种移位寄存器。

- 串行输入 − 串行输出移位寄存器

- 串行输入 − 并行输出移位寄存器

- 并行输入 − 串行输出移位寄存器

- 并行输入 −并行输出移位寄存器

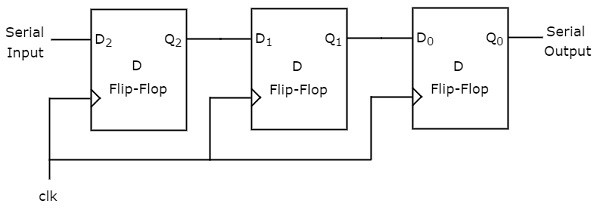

串行输入 − 串行输出 (SISO) 移位寄存器

允许串行输入并产生串行输出的移位寄存器称为串行输入 - 串行输出(SISO)移位寄存器。下图显示了 3 位 SISO 移位寄存器的框图。

该框图由三个级联的 D 触发器组成。这意味着,一个 D 触发器的输出作为下一个 D 触发器的输入连接。所有这些触发器彼此同步,因为每个触发器都应用了相同的时钟信号。

在此移位寄存器中,我们可以从最左边的 D 触发器的输入串行发送位。因此,此输入也称为串行输入。对于时钟信号的每个正边沿触发,数据都会从一个阶段移至下一个阶段。因此,我们可以从最右边的 D 触发器的输出串行接收位。因此,此输出也称为串行输出。

示例

让我们通过在输入端将二进制信息"011"从 LSB 串行发送到 MSB 来查看 3 位 SISO 移位寄存器的工作原理。

假设从最左边到最右边的 D 触发器的初始状态为 $Q_{2}Q_{1}Q_{0}=000$。我们可以从下表中了解3位SISO移位寄存器的工作原理。

| 时钟上升沿数量 | 串行输入 | Q2 | Q1 | Q0 |

|---|---|---|---|---|

| 0 | - | 0 | 0 | 0 |

| 1 | 1(LSB) | 1 | 0 | 0 |

| 2 | 1 | 1 | 1 | 0 |

| 3 | 0(MSB) | 0 | 1 | 1(LSB) |

| 4 | - | - | 0 | 1 |

| 5 | - | - | - | 0(MSB) |

在没有时钟信号的情况下,D 触发器的初始状态为 $Q_{2}Q_{1}Q_{0}=000$。此处,串行输出来自 $Q_{0}$。因此,LSB (1) 在时钟的第 3 个正沿接收,而 MSB (0) 在时钟的第 5 个正沿接收。

因此,3 位 SISO 移位寄存器需要五个时钟脉冲才能产生有效输出。类似地,N 位 SISO 移位寄存器需要 2N-1 个时钟脉冲才能移位"N"位信息。

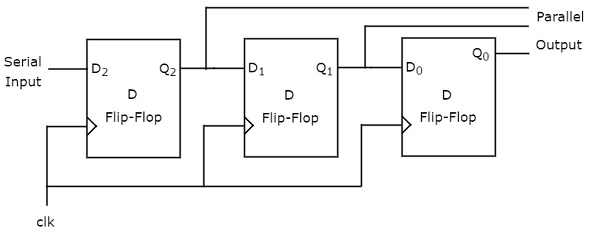

串行输入 - 并行输出 (SIPO) 移位寄存器

允许串行输入并产生并行输出的移位寄存器称为串行输入 - 并行输出(SIPO)移位寄存器。下图显示了 3 位 SIPO 移位寄存器的框图。

该电路由三个级联的 D 触发器组成。这意味着,一个 D 触发器的输出作为下一个 D 触发器的输入连接。所有这些触发器彼此同步,因为每个触发器都应用了相同的时钟信号。

在此移位寄存器中,我们可以从最左边的 D 触发器的输入串行发送位。因此,此输入也称为串行输入。对于时钟信号的每个正边沿触发,数据从一个阶段移位到下一个阶段。在这种情况下,我们可以并行访问每个 D 触发器的输出。因此,我们将从该移位寄存器获得并行输出。

示例

让我们通过在输入端将二进制信息"011"从 LSB 串行发送到 MSB 来查看 3 位 SIPO 移位寄存器的工作原理。

假设从最左边到最右边的 D 触发器的初始状态为 $Q_{2}Q_{1}Q_{0}=000$。这里,$Q_{2}$ 和 $Q_{0}$ 分别是 MSB 和 LSB。我们可以从下表中了解3位SIPO移位寄存器的工作原理。

| 时钟上升沿数 | 串行输入 | Q2(MSB) | Q1 | Q0(LSB) |

|---|---|---|---|---|

| 0 | - | 0 | 0 | 0 |

| 1 | 1(LSB) | 1 | 0 | 0 |

| 2 | 1 | 1 | 1 | 0 |

| 3 | 0(MSB) | 0 | 1 | 1 |

在没有时钟信号的情况下,D 触发器的初始状态为 $Q_{2}Q_{1}Q_{0}=000$。在时钟的第三个正沿,在 D 触发器的输出端并行获得二进制信息 "011"。

因此,3 位 SIPO 移位寄存器需要三个时钟脉冲才能产生有效输出。同样,N 位 SIPO 移位寄存器需要 N 个时钟脉冲才能移位"N"位信息。

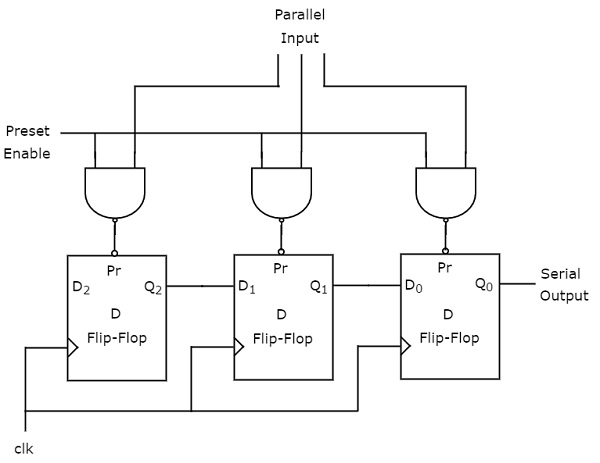

并行输入 − 串行输出 (PISO) 移位寄存器

允许并行输入并产生串行输出的移位寄存器称为并行输入 − 串行输出(PISO)移位寄存器。下图显示了 3 位 PISO 移位寄存器的框图。

该电路由三个级联的 D 触发器组成。这意味着,一个 D 触发器的输出作为下一个 D 触发器的输入连接。所有这些触发器彼此同步,因为每个触发器都应用相同的时钟信号。

在此移位寄存器中,我们可以通过将预设启用设置为 1 来将并行输入应用于每个 D 触发器。对于时钟信号的每个正边沿触发,数据都会从一个阶段移位到下一个阶段。因此,我们将从最右边的 D 触发器获得串行输出。

示例

让我们通过预设输入并行应用二进制信息"011"来查看 3 位 PISO 移位寄存器的工作原理。

由于预设输入是在时钟正沿之前应用的,因此从最左边到最右边的 D 触发器的初始状态将是 $Q_{2}Q_{1}Q_{0}=011$。我们可以从下表中了解3 位 PISO 移位寄存器的工作原理。

| 时钟正沿数量 | Q2 | Q1 | Q0 |

|---|---|---|---|

| 0 | 0 | 1 | 1(LSB) |

| 1 | - | 0 | 1 |

| 2 | - | - | 0(LSB) |

此处,串行输出来自 $Q_{0}$。因此,在应用时钟正沿之前接收 LSB (1),在时钟的第 2 个正沿接收 MSB (0)。

因此,3 位 PISO 移位寄存器需要两个时钟脉冲才能产生有效输出。类似地,N 位 PISO 移位寄存器需要 N-1 个时钟脉冲才能移位"N"位信息。

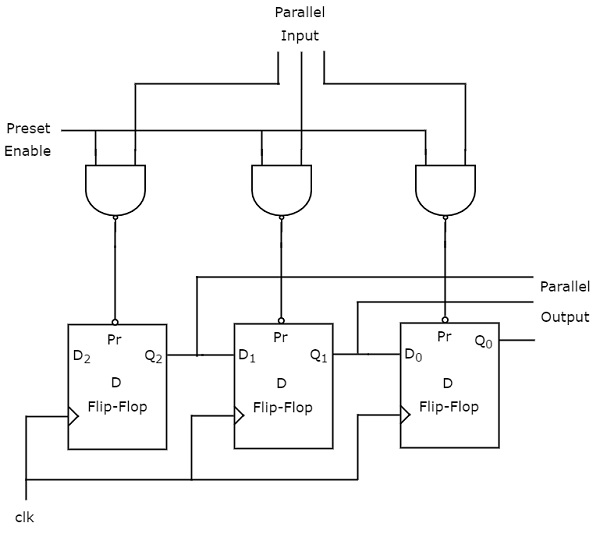

并行输入 - 并行输出 (PIPO) 移位寄存器

允许并行输入并产生并行输出的移位寄存器称为并行输入 - 并行输出(PIPO)移位寄存器。下图显示了 3 位 PIPO 移位寄存器的框图。

该电路由三个级联的 D 触发器组成。这意味着,一个 D 触发器的输出作为下一个 D 触发器的输入连接。所有这些触发器彼此同步,因为每个触发器都应用相同的时钟信号。

在此移位寄存器中,我们可以通过将 Preset Enable 设置为 1 来将并行输入应用于每个 D 触发器。我们可以通过预设或清除来应用并行输入。这两个是异步输入。这意味着,触发器根据异步输入的值产生相应的输出。在这种情况下,输出的影响与时钟转换无关。因此,我们将从每个 D 触发器获得并行输出。

示例

让我们通过预设输入并行应用二进制信息"011"来了解 3 位 PIPO 移位寄存器的工作原理。

由于预设输入是在时钟正沿之前应用的,因此从最左边到最右边的 D 触发器的初始状态将是 $Q_{2}Q_{1}Q_{0}=011$。因此,在应用时钟正沿之前,在 D 触发器的输出端并行获得二进制信息"011"。

因此,3 位 PIPO 移位寄存器需要零时钟脉冲才能产生有效输出。同样,N 位 PIPO 移位寄存器不需要任何时钟脉冲来移位"N"位信息。